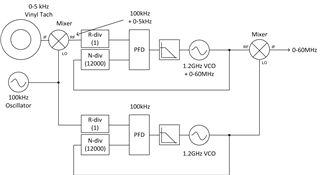

我有一个免费的软件和硬件项目 (RAM 拼盘混合)、它需要一个低频 源振荡器将其频率乘以12000 次。 这可能是 DDS 或 VCO+PLL 的良好应用。

源振荡器的范围介于0Hz 和5kHz 之间。 源振荡器(f0)最常见的速率为1kHz。

12000倍频器的含义是目标输出信号频率为0Hz 至60MHz。 不需要精确的0Hz 输出、但可以实现。 非常需要接近0Hz、但1Hz 或10Hz 是可以的。

由于拼盘是由人类连接的、因此源音在其改变能力方面受到极大的限制。 因此、源振荡器的变化率很慢。 例如、 正常的变化率受人员手移动速度的限制、该速度可能为每秒1或2 kHz。

当源振荡器处于闲置状态时、无需进行极端抖动控制、因为拼盘是一个重飞轮(转盘盘)、这应该能够减少源振荡器信号中的特定抖动量。 但是、如果可以减少抖动、这将是一个优势。