Other Parts Discussed in Thread: DAC38RF89

您好,

我将 DAC38RF89的 JESD204B 配置 为允许。

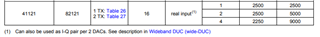

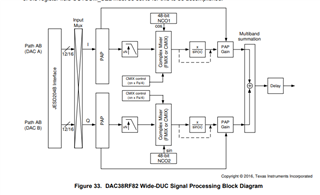

它 用作每2个 DAC 的 I-Q 对。 我 使用 DACA、 Q 使用 DACB。

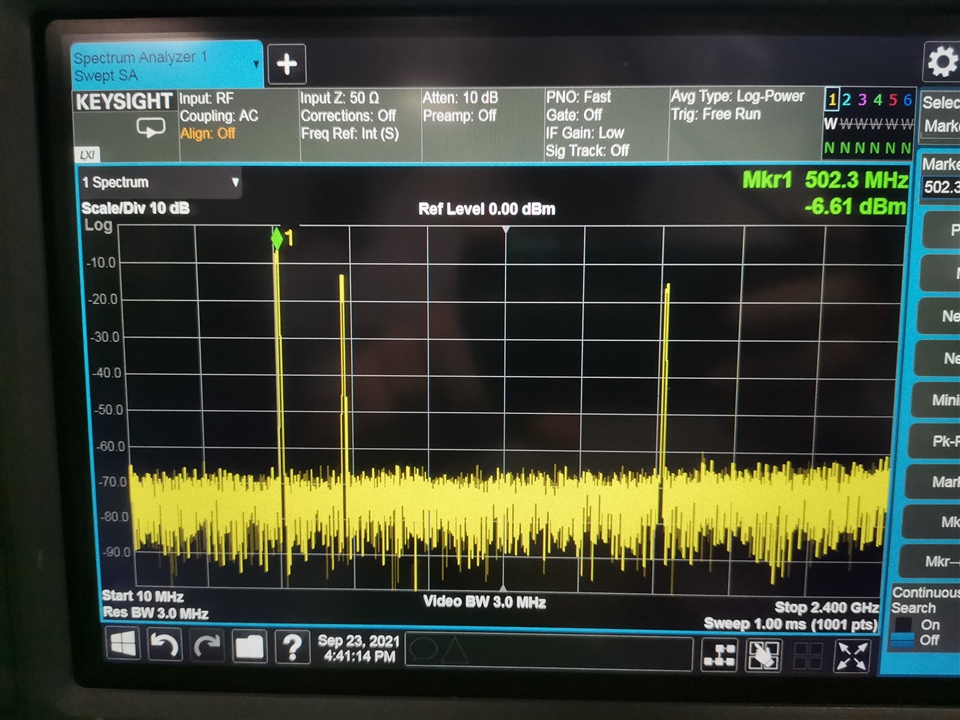

我将 I-Q 数据发送到 DUC 输入、例如输入频率为500MHz、NCOFREQUENCY 为1.2GHz。 当我使用光谱仪观察时、有两条对称的光谱线、分别为1.7GHz 和700MHz。

我想知道原因?以及 在多次复位?后、DUC 后的输出频率如何正确

此致、

福克斯