您好,

我将 DAC38RF89的 JESD204B 配置 为允许。

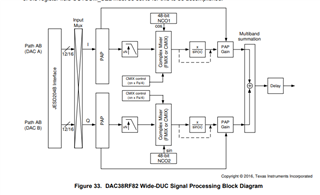

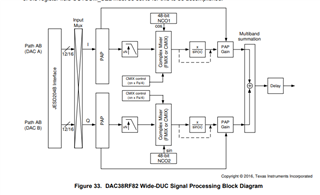

它 用作每2个 DAC 的 I-Q 对。 我 使用 DACA、 Q 使用 DACB。

我将 I-Q 数据发送到 DUC 输入、例如输入频率为500MHz、NCOFREQUENCY 为1.2GHz。 当我使用光谱仪观察时、有两条对称的光谱线、分别为1.7GHz 和700MHz。

我想知道原因?以及 在多次复位?后、DUC 后的输出频率如何正确

此致、

福克斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我将 DAC38RF89的 JESD204B 配置 为允许。

它 用作每2个 DAC 的 I-Q 对。 我 使用 DACA、 Q 使用 DACB。

我将 I-Q 数据发送到 DUC 输入、例如输入频率为500MHz、NCOFREQUENCY 为1.2GHz。 当我使用光谱仪观察时、有两条对称的光谱线、分别为1.7GHz 和700MHz。

我想知道原因?以及 在多次复位?后、DUC 后的输出频率如何正确

此致、

福克斯

您好!

您可能只需要重置 NCO。 有关详细信息、请参阅以下链接

您好!

我向 FPGA 的 ILA 观测接口添加了 IQ 信号并导出了 csv 数据。 高速数据转换器软件会分析 csv 数据、以证明 I-way 数据和 Q-way 数据是完美的正交数据。 我仍然怀疑 nco1和 nco2相位之间的差异导致了这个问题。奇怪的是、问题有时出现、有时消失而不修改任何配置。与 NCO 同步相关的寄存器已经被修改了几次。 FPGA 生成的 IQ 数据的相位也得到保证。 仍然无法保证不会发生错误。 也许我们还可以了解其他一些原因吗?

福克斯

`define DA38RF89

//`define SERDES_PLL_SOURCED_BY_PLL

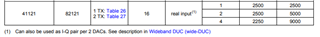

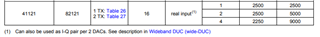

//--for 41121 and 82121 tx2:

//--CLOCK PHASES=01,INTERP=00001,CLKJESD_DIV=0001,CLKJESD_OUT_DIV=0001;

//--L_M1=00011,F_M1=00,M_M1=00,S_M1=00001,HD=1,N_M1/N'_M1=01111

//--RESET config,

//--reset SPI registers;turn on the alarm pin;turn on the dividers;

//cause fuse autoload;set ONE_DAC_ONLY and ONE_LINK_ONLY;

//puts DAC1 and DAC2 into intilization state

`define ADDR_000 7'h00

//`define DATA_000 16'h7060

`define DATA_000 16'h7800

//--vendor ID and Chip Version register,check if AUTOLOAD_DONE is asserted

`define ADDR_FFF 7'h7f

`define DATA_FFF 16'h8009

//--page set register, set general configuration registers

`define ADDR_001 7'h09

`define DATA_001 16'h0000

//--IO_CONFIG

//--SYSREF align to R1 and R3 count---READ ONLY

`define ADDR_002 7'h78

`define DATA_002 16'h0000

//--SYSREF phase count 1 and 2--------READ ONLY

`define ADDR_003 7'h79

`define DATA_003 16'h0000

//--SYSREF phase count 3 and 4--------READ ONLY

`define ADDR_004 7'h7a

`define DATA_004 16'h0000

//--disable 4-pin SPI;disable analog test

`define ADDR_005 7'h01

`define DATA_005 16'h3000

//--temperature sensor and pll loop voltage, read only

`define ADDR_006 7'h06

`define DATA_006 16'h0000

//-------Miscellaneous Configuration Registers--------//

//--page set register, set DIG_MISC

`define ADDR_007 7'h09

`define DATA_007 16'h0004

//--clock configuration register

//sysref is used to sync clock divider or not,should be disabled after intial syncing----------IMPORTANT

//div4 clock;dummy data generation enable;quarter rate clock;

`define ADDR_008 7'h0a

`define DATA_008 16'h7c03

//`define DATA_008 16'hfc03

//--sleep config

//many sleep enable

`define ADDR_009 7'h0b

`define DATA_009 16'h0000

//--divided output clock configuration

//clk_tx is not connected;

`define ADDR_00A 7'h0c

//`define DATA_00A 16'h2001 //CAUTION:select external reference(sysref?)

`define DATA_00A 16'ha002

//--DAC fullscale current register

//10mA + 2mA*[15:12]

`define ADDR_00B 7'h0d

`define DATA_00B 16'hF000

//--internal SYSREF generator register

//LCM:least common multiple,page126,9.2.4

`define ADDR_00C 7'h10

//`define DATA_00C 16'h0001

`define DATA_00C 16'h0000

//--counter for internal SYSREF generator

//LCMGEN_DIV

`define ADDR_00D 7'h11

`define DATA_00D 16'h0000

//--SPI SYSREF for internal SYSREF generator

//LCMGEN_DIV

`define ADDR_00E 7'h12

`define DATA_00E 16'h0000

//--digital test signals register

//select the signal which comes out of the ALARM pin

`define ADDR_00F 7'h1B

`define DATA_00F 16'h0200

//--sleep pin control register

//control the routing of SLEEP pin to different blocks

`define ADDR_010 7'h23

`define DATA_010 16'hffff

//--SYSREF capture circuit control register

//sysref phase window

//sysref align delay

//sysref status enable

//sysref align sysnc

//sysref align bypass

`define ADDR_011 7'h24

`define DATA_011 16'hd800

`define DATA_011_DIST 16'hd800

//--clock input and PLL configuration

//extclk diff or se select

//pll reset

//pll N divider is synced by SYSREF or not

//DACCLK_P/N is used as reference to PLL or directly as DAC clock

//PLL cp sleep

//PLL N divider = 1

//PLL lock detector sensitivity

`define ADDR_012 7'h31 //PLL_ENA=1

`define DATA_012 16'h0400

//PLL configuration 1 register

//VCO feedback divider---M divider = 4,total divider = 16;4.8GHz/16 = 300MHz refin

//not used in external CLK mode

//VCO amplitude

`define ADDR_013 7'h32

`define DATA_013 16'h0308

//PLL configuration 2 register

//PLL vco select--select VCO1

//vco freq range---need further attention

//charge pump current,0x6 fro M=4

`define ADDR_014 7'h33

`define DATA_014 16'h2A18

//LVDS output configuration register

//LVDS output current;

//SYNC0~ powerdown;

//charge pump current

`define ADDR_015 7'h34

`define DATA_015 16'h0000 //CAUTION! [8]=SYNC0 LVDS powerdown

//Fuse Farm clock divider register

`define ADDR_016 7'h35

`define DATA_016 16'h0018

//SERDES clock configuration register

//SERDES_CLK_SEL = DACCLK pad

//SERDES_REFCLK_DIV = 0,divider = 1;

//PREDIVIDER = 1;

//serdes_refclk = 300MHz for DACCLK pad,600MHz for PLL

//16'h0000 for 300MHz DACCLK pad,300MHz/1(SERDES_REFCLK_PREDIV)/1(SERDES_REFCLK_DIV)=300MHz

//16'hF802 for 600MHz PLL clk,4.8GHz/8=600MHz

`define ADDR_017 7'h3B

`ifdef SERDES_PLL_SOURCED_BY_PLL

`define DATA_017 16'hb800

`else

`define DATA_017 16'h0000

`endif

//SERDES clock configuration register

//ENDIVCLK = 1;

//CLKBYPASS = 0;

//LB=00;SLEEPPLL=0;

//VRANGE=0,for output > 2.17GHz

//MPY=8'h51,multiplier = 10, refclk 200MHz × 10 = 3GHz,for refclk from PAD

//MPY=8'h28,multiplier = 5, refclk 600MHz × 5 = 3GHz,for refclk from PLL

`define ADDR_018 7'h3C

`ifdef SERDES_PLL_SOURCED_BY_PLL

`define DATA_018 16'h8029

`else

`define DATA_018 16'h8051

`endif

//SERDES configuration 1 register

//TESTPATT = 000;

//enable serdes offset compensation

//equalizer hold;serdes equalizer

//CDR settings

`define ADDR_019 7'h3D

`define DATA_019 16'h0088

//SERDES configuration 2 register

//loss detection enable;

//comma alignment enable;

//RATE = 00,PLL_OUT = 0.25Lane_rate = 3GHz

//BUS_WIDTH = 16bit;

//sleeprx = 0;

`define ADDR_01A 7'h3E

//`define DATA_01A 16'h0905

`define DATA_01A 16'h0909

//SERDES polarity control register

`define ADDR_01B 7'h3F

`define DATA_01B 16'h0000

//JESD204B SYNCB OUTPUT register

`define ADDR_01C 7'h76

`define DATA_01C 16'h0000

//ALARM SD LOSDET

`define ADDR_01D 7'h04

`define DATA_01D 16'h0000

//JESD204B SYNCB OUTPUT register

`define ADDR_01E 7'h76

`define DATA_01E 16'h0000

//JESD204B SYNCB OUTPUT register

`define ADDR_01F 7'h76

`define DATA_01F 16'h0000

//-------multi-DUC1 Configuration Registers--------//

//--page set register, set multi-DUC1

`define ADDR_200 7'h09

`define DATA_200 16'h0001

//--multi-DUC configuration(PAP,interpolation)

`define ADDR_201 7'h0A

//`define DATA_021 16'h0040 //CAUTION! alarm can zero the data out of JESD block

`define DATA_201 16'h6110

//--multi-DUC configuration(Mixers)

//--NCOAB_ENA=1

`define ADDR_202 7'h0C

`define DATA_202 16'h2622

//--JESD FIFO control

`define ADDR_203 7'h0D

`define DATA_203 16'h0000

//--alarm mask 1 register

`define ADDR_204 7'h0E

`define DATA_204 16'h00ff

//--alarm mask 2 register

`define ADDR_205 7'h0f

`define DATA_205 16'hffff

//--alarm mask 3 register

//LCMGEN_DIV

`define ADDR_206 7'h10

`define DATA_206 16'hffff

//--alarm mask 4 register

`define ADDR_207 7'h11

`define DATA_207 16'hffff

//--JESD Lane skew(read-only)

`define ADDR_208 7'h12

`define DATA_208 16'h0000

//--CMIX configuration

//--coarse mixer disabled

`define ADDR_209 7'h17

`define DATA_209 16'h0000

//--SYSREF capture circuit control register

//output delay,outsum_sel

//--bit0 and bit2 are set

`define ADDR_20A 7'h19

`define DATA_20A 16'h0005

//--sysref use for clock divider--set [6:4] to 3'b000 for startup sequence in datasheet P124

`define ADDR_20B 7'h24

`define DATA_20B 16'h0000

//serdes clock control

//CLKJESD_DIV,CLKJESD_OUT_DIV,values from table 38

`define ADDR_20C 7'h25

`define DATA_20C 16'h1100

//sync source control 1 register

`define ADDR_20D 7'h27

`define DATA_20D 16'h4848

//sync source control 2 register

`define ADDR_20E 7'h28

`define DATA_20E 16'h0330

`define ADDR_20F 7'h29

`define DATA_20F 16'h0000

`define ADDR_210 7'h2A

`define DATA_210 16'h0000

`define ADDR_211 7'h2B

`define DATA_211 16'h0000

`define ADDR_212 7'h2C

`define DATA_212 16'h0000

`define ADDR_213 7'h2D

`define DATA_213 16'h1FFF

`define ADDR_214 7'h2E

`define DATA_214 16'h1FFF

//DAC SPI configuration register

`define ADDR_215 7'h2F

`define DATA_215 16'h0000

//DAC SPI constant register

`define ADDR_216 7'h30

`define DATA_216 16'h0000

//Gain for path AB register

`define ADDR_217 7'h32

`define DATA_217 16'h8800

//Gain for path CD register

`define ADDR_218 7'h33

`define DATA_218 16'h0400

//JESD error counter(read-only)

`define ADDR_219 7'h41

`define DATA_219 16'h0000

//JESD subclass register

`define ADDR_21A 7'h48

`define DATA_21A 16'h31c3

//JESD lane enable register

//enable the lanes;

//reperting D21.5/K28.5/ILAS verify for test purpose

`define ADDR_21B 7'h4A

`define DATA_21B 16'h0f01

//JESD RBD buffer and frame octets(F) register

//F is set to 1 here for LMFSH=82121

`define ADDR_21C 7'h4B

`define DATA_21C 16'h1300

//JESD K and L parameters

//K is set to 20 and L is set to 4 here

`define ADDR_21D 7'h4c

`define DATA_21D 16'h1303

//JESD M and S parameters

//M is set to 1 and S is set to 2 here

`define ADDR_21E 7'h4d

`define DATA_21E 16'h0001

//JESD N,HD and SCR parameters

//N' is set to 16,HD is set to 0,N is set to 16 here

`define ADDR_21F 7'h4e

`define DATA_21F 16'h0F4F

//JESD character match and other register

`define ADDR_220 7'h4f

`define DATA_220 16'h1c60

//JESD link configuration data register

`define ADDR_221 7'h50

`define DATA_221 16'h0000

//JESD sync request register

`define ADDR_222 7'h51

`define DATA_222 16'h00FF

//JESD error output register

`define ADDR_223 7'h52

`define DATA_223 16'h00FF

//JESD ILA check 1 register

//ILA_M = 1 and ILA_F = 3

`define ADDR_224 7'h53

`define DATA_224 16'h0100

//JESD ILA check 2 register

//ILA_HD = 0,ILA_L = 4,ILA_K=20,ILA_S=8

`define ADDR_225 7'h54

`define DATA_225 16'h8e60

//JESD sysref mode register----[2:0]==3'b000 for start up sequence in datasheet P124

`define ADDR_226 7'h5C

`define DATA_226 16'h0000

//--NCO freq path AB reg1

`define ADDR_227 7'h1E

`define DATA_227 16'h0000

//--NCO freq path AB reg2

`define ADDR_228 7'h1F

`define DATA_228 16'h0000

//--NCO freq path AB reg3 ------fs/4

`define ADDR_229 7'h20

`define DATA_229 16'h4000

//--NCO freq path CD reg1

`define ADDR_22A 7'h21

`define DATA_22A 16'h0000

//--NCO freq path CD reg2

`define ADDR_22B 7'h22

`define DATA_22B 16'h0000

//--NCO freq path CD reg3 ------fs/4

`define ADDR_22C 7'h23

`define DATA_22C 16'h0000

//--NCO phase path AB(autosync) ------0 degree

`define ADDR_22D 7'h1C

`define DATA_22D 16'h0000

//--NCO phase path CD(autosync)

`define ADDR_22E 7'h1D

`define DATA_22E 16'h0000

//--CROSSBAR 1,lane mapping

`define ADDR_22F 7'h5F

`define DATA_22F 16'h0123

//--CROSSBAR 2,lane mapping

`define ADDR_230 7'h60

`define DATA_230 16'h4567

//-------multi-DUC2 Configuration Registers--------//

//--page set register, set multi-DUC2

`define ADDR_300 7'h09

`define DATA_300 16'h0002

//--multi-DUC configuration(PAP,interpolation)

`define ADDR_301 7'h0A

//`define DATA_021 16'h0040 //CAUTION! alarm can zero the data out of JESD block

`define DATA_301 16'h6110

//--multi-DUC configuration(Mixers)

//--NCOAB_ENA=1

`define ADDR_302 7'h0C

`define DATA_302 16'h2622

//--JESD FIFO control

`define ADDR_303 7'h0D

`define DATA_303 16'h0000

//--alarm mask 1 register

`define ADDR_304 7'h0E

`define DATA_304 16'h00ff

//--alarm mask 2 register

`define ADDR_305 7'h0f

`define DATA_305 16'hffff

//--alarm mask 3 register

//LCMGEN_DIV

`define ADDR_306 7'h10

`define DATA_306 16'hffff

//--alarm mask 4 register

`define ADDR_307 7'h11

`define DATA_307 16'hffff

//--JESD Lane skew(read-only)

`define ADDR_308 7'h12

`define DATA_308 16'h0000

//--CMIX configuration

//--coarse mixer disabled

`define ADDR_309 7'h17

`define DATA_309 16'h0000

//--SYSREF capture circuit control register

//output delay,outsum_sel

//--bit0 and bit2 are set

`define ADDR_30A 7'h19

`define DATA_30A 16'h0000

//--sysref use for clock divider--set [6:4] to 3'b000 for startup sequence in datasheet P124

`define ADDR_30B 7'h24

`define DATA_30B 16'h0000

//serdes clock control

//CLKJESD_DIV,CLKJESD_OUT_DIV,values from table 38

`define ADDR_30C 7'h25

`define DATA_30C 16'h1100

//sync source control 1 register

`define ADDR_30D 7'h27

`define DATA_30D 16'h4848

//sync source control 2 register

`define ADDR_30E 7'h28

`define DATA_30E 16'h0330

`define ADDR_30F 7'h29

`define DATA_30F 16'h0000

`define ADDR_310 7'h2A

`define DATA_310 16'h0000

`define ADDR_311 7'h2B

`define DATA_311 16'h0000

`define ADDR_312 7'h2C

`define DATA_312 16'h0000

`define ADDR_313 7'h2D

`define DATA_313 16'h1FFF

`define ADDR_314 7'h2E

`define DATA_314 16'h1FFF

//DAC SPI configuration register

`define ADDR_315 7'h2F

`define DATA_315 16'h0000

//DAC SPI constant register

`define ADDR_316 7'h30

`define DATA_316 16'h0000

//Gain for path AB register

`define ADDR_317 7'h32

`define DATA_317 16'h8800

//Gain for path CD register

`define ADDR_318 7'h33

`define DATA_318 16'h0400

//JESD error counter(read-only)

`define ADDR_319 7'h41

`define DATA_319 16'h0000

//JESD subclass register

`define ADDR_31A 7'h48

`define DATA_31A 16'h31c3

//JESD lane enable register

//enable the lanes;

//reperting D21.5/K28.5/ILAS verify for test purpose

`define ADDR_31B 7'h4A

`define DATA_31B 16'hF001

//JESD RBD buffer and frame octets(F) register

//F is set to 2 here for LMFSH=82380

`define ADDR_31C 7'h4B

`define DATA_31C 16'h1300

//JESD K and L parameters

//K is set to 20 and L is set to 3 here

`define ADDR_31D 7'h4c

`define DATA_31D 16'h1303

//JESD M and S parameters

//M is set to 1 and S is set to 2 here

`define ADDR_31E 7'h4d

`define DATA_31E 16'h0001

//JESD N,HD and SCR parameters

//N' is set to 16,HD is set to 0,N is set to 16 here

`define ADDR_31F 7'h4e

`define DATA_31F 16'h0F4F

//JESD character match and other register

`define ADDR_320 7'h4f

`define DATA_320 16'h1c60

//JESD link configuration data register

`define ADDR_321 7'h50

`define DATA_321 16'h0000

//JESD sync request register

`define ADDR_322 7'h51

`define DATA_322 16'h00FF

//JESD error output register

`define ADDR_323 7'h52

`define DATA_323 16'h00FF

//JESD ILA check 1 register

//ILA_M = 1 and ILA_F = 3

`define ADDR_324 7'h53

`define DATA_324 16'h0100

//JESD ILA check 2 register

//ILA_HD = 0,ILA_L = 4,ILA_K=20,ILA_S=8

`define ADDR_325 7'h54

`define DATA_325 16'h8e60

//JESD sysref mode register----[2:0]==3'b000 for start up sequence in datasheet P124

`define ADDR_326 7'h5C

`define DATA_326 16'h0000

//--NCO freq path AB reg1

`define ADDR_327 7'h1E

`define DATA_327 16'h0000

//--NCO freq path AB reg2

`define ADDR_328 7'h1F

`define DATA_328 16'h0000

//--NCO freq path AB reg3 ------fs/4

`define ADDR_329 7'h20

`define DATA_329 16'h4000

//--NCO freq path CD reg1

`define ADDR_32A 7'h21

`define DATA_32A 16'h0000

//--NCO freq path CD reg2

`define ADDR_32B 7'h22

`define DATA_32B 16'h0000

//--NCO freq path CD reg3 ------fs/4

`define ADDR_32C 7'h23

`define DATA_32C 16'h0000

//--NCO phase path AB(autosync) ------90 degree

`define ADDR_32D 7'h1C

`define DATA_32D 16'h4000

//--NCO phase path CD(autosync)

`define ADDR_32E 7'h1D

`define DATA_32E 16'h0000

//--CROSSBAR 1,lane mapping

`define ADDR_32F 7'h5F

`define DATA_32F 16'h4567

//--CROSSBAR 2,lane mapping

`define ADDR_330 7'h60

`define DATA_330 16'h0123

//---lmk_sync should be asserted here to generate at least 2 SYSREF

//-----startup sequence in Page124

//--1ST:reset encoder block

//--SET page4

`define ADDR_03E 7'h09

`define DATA_03E 16'h0004

//--1ST:reset encoder block

//--SET page4 register 0x0A[15] to 1

`define ADDR_03F 7'h0A

`define DATA_03F 16'hfc03

//--SET page4 register 0x0A[15] to 0

`define ADDR_040 7'h0A

`define DATA_040 16'h7c03

//--2ND:put JESD204B core in reset

//--SET page0 register 0x00[1:0] to 2'b11

`define ADDR_041 7'h09

`define DATA_041 16'h0000

//SET page0 register 0x00[1:0] to 2'b11

`define ADDR_042 7'h00

`define DATA_042 16'h7803

//--3RD:sync CDRV and JESD204B blocks

//--SET page1/2 register 0x24[6:4] to 3'b010,use all SYSREF

`define ADDR_043 7'h09

`define DATA_043 16'h0003

//--SET page1/2 register 0x24[6:4] to 3'b010,use only the next SYSREF

`define ADDR_044 7'h24

//`define DATA_044 16'h0020 //use only the next SYSREF

`define DATA_044 16'h0010 //use all SYSREF

//---lmk_sync should be asserted here to generate at least 2 SYSREF

//--SET page1/2 register 0x5c[2:0] to 3'b001,use all SYSREF

`define ADDR_045 7'h5c

`define DATA_045 16'h0011 //use only the next SYSREF

//`define DATA_045 16'h0001 //use all sysref

//---lmk_sync should be asserted here to generate at least 2 SYSREF

//---4TH : take JESD core out of reset

//--SET page0 register 0x00[1:0] to 2'b00

`define ADDR_046 7'h09

`define DATA_046 16'h0000

//SET page0 register 0x00[1:0] to 2'b11

`define ADDR_047 7'h00

`define DATA_047 16'h7800

//---lmk_sync should be asserted here to generate at least 2 SYSREF

//---independent clear miscelloneous mask

//---miscellaneous configuration region

//--page set register, set master page

`define ADDR_048 7'h09

`define DATA_048 16'h0000

//clear serdes loss of signal alarms

`define ADDR_049 7'h04

`define DATA_049 16'h0000

//clear SYSREF alignment circuit alarms

`define ADDR_04A 7'h05

`define DATA_04A 16'h0000

//clear lane single detect alarm MASK

`define ADDR_04B 7'h02

`define DATA_04B 16'h0000

//clear clock alarm MASK

`define ADDR_04C 7'h03

`define DATA_04C 16'h0000

//---independent clear multi-DUC mask

//---multi-DUC configuration region

//--page set register, set multi-DUC page

`define ADDR_04D 7'h09

`define DATA_04D 16'h0003

//JESD alarm for lane0

`define ADDR_04E 7'h64

`define DATA_04E 16'h0000

//JESD alarm for lane1

`define ADDR_04F 7'h65

`define DATA_04F 16'h0000

//JESD alarm for lane2

`define ADDR_050 7'h66

`define DATA_050 16'h0000

//JESD alarm for lane3

`define ADDR_051 7'h67

`define DATA_051 16'h0000

//JESD alarm for lane4

`define ADDR_052 7'h68

`define DATA_052 16'h0000

//JESD alarm for lane5

`define ADDR_053 7'h69

`define DATA_053 16'h0000

//JESD alarm for lane6

`define ADDR_054 7'h6A

`define DATA_054 16'h0000

//JESD alarm for lane7

`define ADDR_055 7'h6B

`define DATA_055 16'h0000

//SYSREF and PAP alarms

`define ADDR_056 7'h6C

`define DATA_056 16'h0000

//clock divider alarms 1 register

`define ADDR_057 7'h6D

`define DATA_057 16'h0000

//------independent,get sysref status

//--page set register, set DIG_MISC

`define ADDR_100 7'h09

`define DATA_100 16'h0004

//--set SYSR_ALIGN_SYNC to clear status

`define ADDR_101 7'h24

`define DATA_101 16'hd802

`define DATA_101_DIST 16'hd802

//--page set register, set general configuration registers

`define ADDR_102 7'h09

`define DATA_102 16'h000

//--ALM_SYSREF_DET

`define ADDR_103 7'h05

`define DATA_103 16'h000

//--SYSREF_ALIGN_R

`define ADDR_104 7'h78

`define DATA_104 16'h000

//--SYSREF12_CNT

`define ADDR_105 7'h79

`define DATA_105 16'h000

//--SYSREF34_CNT

`define ADDR_106 7'h7A

`define DATA_106 16'h000

//--ALM_SD_DET,W0C

`define ADDR_107 7'h04

`define DATA_107 16'h000

//--generate SPI sync

`define ADDR_108 7'h09

`define DATA_108 16'h0003

//--generate SPI sync

`define ADDR_109 7'h28

`define DATA_109 16'h0332

//--generate SPI sync

`define ADDR_10A 7'h28

`define DATA_10A 16'h0330