Other Parts Discussed in Thread: DAC38RF82

尊敬的专家:

美好的一天!

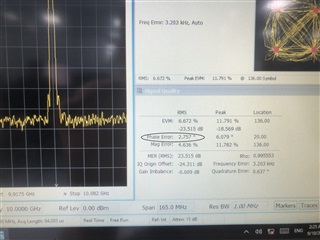

我们的客户使用 DAC38RF82来检查 QPSK 信号,有时,I /Q 阶段 会有很大的偏差,如下面的屏幕截图所示

通常,此值为0.3,但10%将变为2.7。 客户测试了很多芯片,有相同的问题,好像是寄存器设置的原因。

它们将 dac38rf82设置为 82121模式,并将4倍 插值、6.4G 采样率、1.6GHz 数据速率设置为 FPGA 使用 Xilinx XC7VX330T。

您能否根据您的经验提供任何解决方法的建议?

BR、

Leon.Liu