大家好、

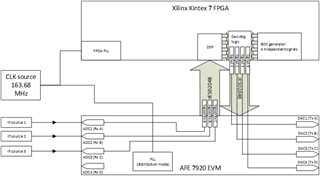

我们最近一直在尝试以以下原理图所示的方式将 AFE7920EVM 连接到类似 Kintex-7的 FPGA (XC7K410T):

为了对 AFE EVM 进行编程、使用了随附的脚本(感谢 TI 的 David Chaparro 的输入)、它能够在 AFE 端进行编译、而不会出现任何错误。

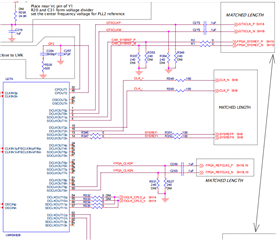

但是、连接的 FPGA 似乎有一些问题、因为它看不到来自 AFE 端的正确时钟。 因此、在调试过程中、我们尝试手动探测 AFE 侧的 LMK 输出、以查看其输出的时钟是否正确(LMK 应处于分配模式、因为其输入为163.68MHz 外部参考时钟、 所有系统相关频率都是其衍生器件)。 根据 LMK 的原理图(见下文)、GTXCLK 输入预计为163.68MHz、FPGA_SYSREF 和 FPGA_REFCLK2输入预期为163.68MHz (在我们的第一个解释中)。

但是、在用示波器进行探测之后、会检测到频率为5.115MHz 的信号、其中5.115是因数163.68 (5.115x32=163.68)。 在深入了解 Latte 代码和工作区后、我发现在以下变量中可以看到相同的数字(5.115):

lmkParams.sysrefFreq 和 AFE.systemStatus.sysrefFreq

无论我做什么、我都不能覆盖它们、以便测量的输出频率与5.115MHz 有任何不同。

TI 员工能否帮助我解决这个5.11数字来自何处以及是否可以并且应该进行修改、以便 LMK 能够在其输出到 FPGA 时提供163.68 MHz 的问题?

此致、

Željko μ A

########## General settings: ##########

# VLBI Tx frequency plan details:

custom_clk = 2

ncoFreqModes = ["1KHz", "FCW"]

Fnco_tx1 = 2245.0

Fnco_rx1 = 500.0

if custom_clk == 0:

f0 = 122.88

Nrx = 24

Nddc = 12

Ntx = 3

NFRef = 4

NfpgaRefClk = 2

NinputClk = 12

LMFSHdRx = ['24410', '24410', '24410', '24410']

LMFSHdFb = ['24410', '24410']

LMFSHdTx = ['24410', '24410', '24410', '24410']

syncLoopBack = False

elif custom_clk == 2:

f0 = 163.68

Nrx = 12

Nddc = 6

Ntx = 3

NFRef = 1

NfpgaRefClk = 1

NinputClk = 1

LMFSHdRx = ['22210', '22210', '22210', '22210']#['44210', '44210', '44210', '44210']

LMFSHdFb = ['22210', '22210']

LMFSHdTx = ['22210', '22210', '22210', '22210']#['44210', '44210', '44210', '44210']

syncLoopBack = False#True#

Nduc = Nddc*Ntx

# AFE general settings

AFE.systemStatus.loadTrims = 1

setupParams.skipFpga = 1

setupParams.fpgaRefClk = f0*NfpgaRefClk

sysParams = AFE.systemParams

sysParams.FRef = f0*NFRef

########## Analog settings: AFE 79XX EVM ##########

# General system settings

sysParams.RRFMode = 0

sysParams.modeTdd = 0

sysParams.adcSelect0 = [0, 1, 2]

sysParams.adcSelect1 = [0, 1, 2]

sysParams.useSpiSysref = 0

sysParams.sysrefTermination = 0

sysParams.ncoFreqMode = ncoFreqModes[custom_clk != 0]

sysParams.spiMode = 1

# ADC settings

sysParams.FadcRx = f0*Nrx

sysParams.rxEnable = [1, 1, 1, 1]

sysParams.externalClockRx = 0

sysParams.halfRateModeRx = [0, 0]

sysParams.ddcFactorRx = [Nddc, Nddc, Nddc, Nddc]

sysParams.numBandsRx = [0, 0, 0, 0]

sysParams.numRxNCO = 1

sysParams.ncoRxMode = [0, 0]

sysParams.broadcastRxNcoSel = 0

sysParams.rxNco0 = [ [Fnco_rx1, Fnco_rx1],

[870.0, 870.0],

[637.5, 637.5],

[637.5, 637.5]]

sysParams.rxNco1 = [ [Fnco_rx1, Fnco_rx1],

[870.0, 870.0],

[637.5, 637.5],

[637.5, 637.5]]

# FB settings

sysParams.FadcFb = sysParams.FadcRx

sysParams.fbEnable = [0, 0]

sysParams.halfRateModeFb = [0, 0]

sysParams.ddcFactorFb = [Nddc, Nddc]

sysParams.numBandsFb = [0, 0]

sysParams.numFbNCO = 1

sysParams.ncoFbMode = 0

sysParams.fbNco0 = [1000, 1000]

sysParams.fbNco1 = [1000, 1000]

sysParams.fbNco2 = [1000, 1000]

sysParams.fbNco3 = [1000, 1000]

# DAC settings

# DAC sampling rate must fall into one of the following frequency ranges (due to pll restrictions): [7.2 GHz, 7.68 GHz] or [8.8 GHz, 9.1 GHz] or [9.7 GHz, 10.24 GHz] or [11.6 GHz, 12.08 GHz]

sysParams.Fdac = sysParams.FadcRx*Ntx

sysParams.txEnable = [1, 1, 1, 1]

sysParams.externalClockTx = 0

sysParams.halfRateModeTx = [0, 0]

sysParams.ducFactorTx = [Nduc, Nduc, Nduc, Nduc]

sysParams.numBandsTx = [0, 0, 0, 0]

sysParams.numTxNCO = 1

sysParams.combineDucMode = [0, 0]

sysParams.enableDacInterleavedMode = 0

sysParams.ncoTxMode = [0, 0]

sysParams.broadcastTxNcoSel = 0

sysParams.txNco0 = [ [Fnco_tx1, Fnco_tx1],

[5020.0, 5020.0],

[8212.5, 8212.5],

[6812.5, 6812.5]]

sysParams.txNco1 = [ [Fnco_tx1, Fnco_tx1],

[5020.0, 5020.0],

[8212.5, 8212.5],

[6812.5, 6812.5]]

########## Clock distribution mode setting ##########

setupParams.skipLmk = 0

lmkParams.pllEn = (custom_clk == 0)

lmkParams.inputClk = f0*NinputClk

lmkParams.sysrefFreq = lmkParams.inputClk#f0*Nrx/1024

lmkParams.lmkFrefClk = 1

lmkParams.lmkPulseSysrefMode = 0

#AFE.systemStatus.sysrefFreq = lmkParams.inputClk

#AFE.LMK.lmkConfig()

########## JESD204 settings AFE 79XX EVM ##########

sysParams.topLevelSystemMode = 'StaticTDDMode'

sysParams.jesdSystemMode = [3, 3]

sysParams.serdesFirmware = 1

sysParams.jesdABLvdsSync = 1

sysParams.jesdCDLvdsSync = 1

sysParams.syncLoopBack = syncLoopBack

sysParams.jesdLoopbackEn = 1

sysParams.setIlaParams = 1

sysParams.jesdTxIlaM = [8, 8, 2, 8, 8, 2]

sysParams.jesdTxIlaLid = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.jesdTxIlaL = [4, 4, 2, 4, 4, 2]

sysParams.LMFSHdRx = LMFSHdRx

sysParams.jesdRxProtocol = [0, 0]

sysParams.jesdRxLaneMux = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.jesdRxRbd = [4, 4]

sysParams.rxJesdTxScr = [1, 1, 1, 1]

sysParams.rxJesdTxK = [16, 16, 16, 16]

sysParams.rxJesdTxSyncMux = [0, 0, 0, 0]

sysParams.rxDataMux = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.serdesRxLanePolarity = [0, 0, 0, 0, 0, 0, 0, 0]

sysParams.adcDataMuxEn = 0

sysParams.LMFSHdFb = LMFSHdFb

sysParams.fbJesdTxScr = [1, 1]

sysParams.fbJesdTxK = [16, 16]

sysParams.fbJesdTxSyncMux = [0, 0]

sysParams.fbDataMux = [0, 1]

sysParams.LMFSHdTx = LMFSHdTx

sysParams.jesdTxProtocol = [0, 0]

sysParams.jesdTxLaneMux = [0, 1, 2, 3, 4, 5, 6, 7]

#sysParams.jesdTxRbd = [4, 4]

sysParams.jesdRxScr = [1, 1, 1, 1]

sysParams.jesdRxK = [16, 16, 16, 16]

sysParams.jesdRxSyncMux = [0, 0, 0, 0]

sysParams.txDataMux = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.serdesTxLanePolarity = [0, 0, 0, 0, 0, 0, 0, 0]

#sysParams.dacDataMuxEn = 0

#sysParams.serdesTxPreCursor = [6, 6, 6, 6, 6, 6, 6, 6]

#sysParams.serdesTxPostCursor = [0, 0, 0, 0, 0, 0, 0, 0]

#sysParams.serdesTxMainCursor = [3, 0, 0, 0, 0, 0, 0, 3]

########## Dummy txt ##########

sysParams.gpioMapping={ 'H8': 'ADC_SYNC0',

'H7': 'ADC_SYNC1',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'DAC_SYNC0',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

lmk.rawWriteLogEn = 1

lmk.logEn = 1

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat = 0x01

logDumpInst.rewriteFile = 1

logDumpInst.rewriteFileFormat4 = 1

device.optimizeWrites = 0

device.rawWriteLogEn = 1

device.delay_time = 0

AFE.deviceBringup()

AFE.TOP.overrideTdd(15,3,15)

AFE.saveCAfeParamsFile()