主题中讨论的其他器件: AFE7900

尊敬的支持部门:

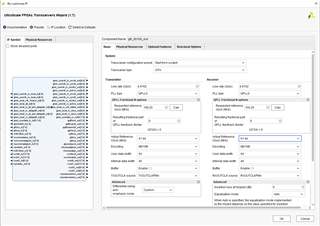

我已经创建了该线程来聚合我的部分问题。 我有一个 AFE7900EVM 板和一个用于参数评估的 ZCU102板。 我现在需要使用全部4个 ADC 通道操作 AD 转换器、并且抽取率= 48。 对于 LMK 和 AFE7900配置、我使用 AFE79xx GUI (Latte)、对于 ZCU102、使用提供的参考设计。 该参考设计(DDC = 4、拉速率= 12Gbps、64/66编码等)效果良好。

我的问题是:需要在 JESD204 TI IP 和 GTH 端以及 AFE79xx 内的 Python 中修改哪些内容? 我的所有尝试都失败了、而且链接从未建立。

例如:

1) Lanerate shoud 为 4.9152 Gbps (正确吗?)

2) FPGA 参考 时钟应该是 61.44MHz (但我无法在 Latte GUI 中达到此值-出现错误消息)

3) 3)通道= 2

4) 4)编码= 8B10B

5)以及其他参数如何? (E., F, K,...).

感谢您的建议。