是否有包含 AFE7900的 LMFS 与 JESD204B 的映射表及其线数据宽度(32/64位)的映射表?

目前在 FPGA 端使用 TI-204C IP、但我不知道如何映射(DAC/ADC) IQ 数据。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的明峰:

您正在使用的 JESD 模式的 LMFS 是多少? 对于给定的 LMFS、 根据 JESD204C 规范、只有一种可能的帧格式。 使用 TI JESD IP 时、LANE_DATA_WIDTH 由 204C-IP 的"RX_LN_DATA_WIDTH"和"TX_LN_DATA_WIDTH"参数进行设置。 该设置默认为64。 有关详细信息、请参阅 IP 用户指南。

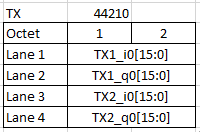

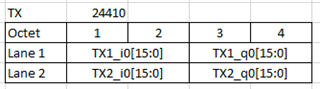

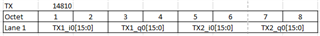

一些常用模式的帧格式:

此致、

维贾伊

我的 JESD 和 LMFS 模式是 JESD204B/24410、我将问题分为 三个部分:

如果将 TX_LN_DATA_WIDTH 设置为32位、则 TX_LANE_DATA[31:0]中 tx1_i0[15:0]、tx1_Q0[15:0]的排列关系是什么?

如果将 TX_LN_DATA_WIDTH 设置为64位、则 TX_LANE_DATA[63:0]中 tx1_i0[15:0]、tx1_Q0[15:0]的排列关系是什么?

3.AFE7900是14位的 DAC/ADC。如何在16位的线路数据中排列14位的 IQ 数据?例如:assign tx1_i0[15:0]={i[13:0]、2'b0};或 assign tx1_i0[15:0]={2'b0、i[13:0]};

谢谢你!

尊敬的明峰:

1.由于24410模式下的帧为32位宽、LN_DATA_WIDTH 设置为32、因此 TX_LANE_DATA[31:0]中将有一个帧数据。

2.如果 LN_DATA_WIDTH 设置为64、则 TX_LANE_DATA[63:0]中将有两个帧数据。

3. 如 帧格式所示,JESD 接口处的复杂数据样本 为16位宽。

在 Tx 信号链中、来自 JESD 块 的输入具有16位分辨率。 但在发送到射频 DAC 之前、内插块输出将舍入为14位分辨率。

在 Rx 信号链中、射频 ADC 的输出具有14位 分辨率。 但 DDC 的输出具有16位分辨率。 由于 抽取后 SNR 较高、因此 使用了更高的分辨率。

此致、

维贾伊