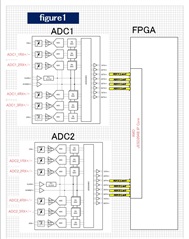

FPGA 和 ADC1 (AFE7906)与 ADC2 (AFE7906)连接。

我想配置 MUX、如图1所示。

将 ADC1_1RX 的 ADC 输入数据输出到 ADC1_LANE1 (3stx)

将 ADC1_2RX 的 ADC 输入数据输出到 ADC1_Lane2 (4stx)

将 ADC1_3RX 的 ADC 输入数据输出到 ADC1_Lane3 (5stx)

将 ADC1_4RX 的 ADC 输入数据输出到 ADC1_Lane4 (6stx)

将 ADC2_1RX 的 ADC 输入数据输出到 ADC2_Lane1 (3stx)

将 ADC2_2RX 的 ADC 输入数据输出到 ADC2_Lane2 (4stx)

将 ADC2_3RX 的 ADC 输入数据输出到 ADC2_Lane3 (5stx)

将 ADC2_4RX 的 ADC 输入数据输出到 ADC2_Lane4 (6stx)

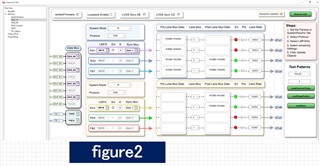

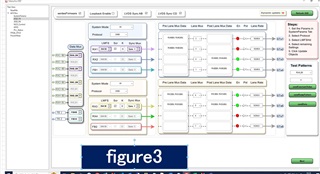

哪种 MUX 配置更好、如图2或图3所示?

对于图2和图3、当将 RAMP 测试设置为 Latte 中的 ADC1和 ADC2时

AFE.JESD.ADCJESD[0].adcRampTestPattern (0、1、0)#chNo、en、RampInc:RxA

AFE.JESD.ADCJESD[0].adcRampTestPattern (1、1)#chNo、en、RampInc:RxB

AFE.JESD.ADCJESD[1].adcRampTestPattern (0、1、2)#chNo、en、RampInc:RXC

AFE.JESD.ADCJESD[1].adcRampTestPattern (1、1、3)#chNo、en、RampInc:RxD

输出是否与下方类似?

ADC1_Lane1 RampInc 1

ADC1_Lane2 RampInc 2

ADC1_Lane3 RampInc 3

ADC1_Lane4 RampInc 4

ADC2_Lane1 RampInc 1

ADC2_Lane2 RampInc 2

ADC2_Lane3 RampInc 3

ADC2_Lane4 RampInc 4