请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE7900EVM 您好!

我们已修改 ZCU102的参考设计、可用于另一个 ZU+电路板。 从 Latte 编程后、出现以下错误消息:

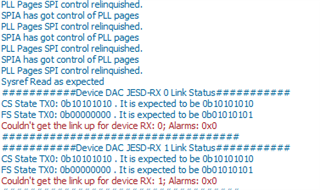

#Executing .. AFE79xx/bringup/TI_IP_10Gbps_8Lane_ConfigLmk.py #Start Time 2023-12-26 17:54:57.291000 The External Sysref Frequency should be an integer factor of: 3.84MHz 2T2R1F Number: 0 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 2T2R1F Number: 1 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 Device Initialization for ChipVersion: 2.0 LMK Clock Divider - Device registers reset. LMK Clock Divider - Device registers reset. REFCLOCK is used from LMK source, ensure board connections are ok to do the same DONOT_OPEN_Atharv_FULL - Device registers reset. chipType: 0xa chipId: 0x78 chipVersion: 0x20 SPIA has got control of PLL pages PLL Pages SPI control relinquished. Fuse farm load autoload done successful No autload error Fuse farm load autoload done successful No autload error patchSize=6677 //Patch Version = 155 //PG Version = 0 //Release Date [dd/mm/yy] = 27/11/21 SPIA has got control of PLL pages PLL Locked PLL Pages SPI control relinquished. SPIA has got control of PLL pages PLL Pages SPI control relinquished. SPIA has got control of PLL pages PLL Pages SPI control relinquished. SPIA has got control of PLL pages PLL Pages SPI control relinquished. Sysref Read as expected ###########Device DAC JESD-RX 0 Link Status########### CS State TX0: 0b10101010 . It is expected to be 0b10101010 FS State TX0: 0b00000000 . It is expected to be 0b01010101 Couldn't get the link up for device RX: 0; Alarms: 0x0 ################################### ###########Device DAC JESD-RX 1 Link Status########### CS State TX0: 0b10101010 . It is expected to be 0b10101010 FS State TX0: 0b00000000 . It is expected to be 0b01010101 Couldn't get the link up for device RX: 1; Alarms: 0x0 ################################### #Done executing .. AFE79xx/bringup/TI_IP_10Gbps_8Lane_ConfigLmk.py #End Time 2023-12-26 17:56:13.144000 #Execution Time = 75.853000164 s #================ ERRORS:2, WARNINGS:1 ================#

JESD-RX 0链路的 CS 状态正确、但 FS 状态不正确、Rx 1链路的 CS 状态也是如此。

此外、它还谈到了 DAC JESD 链路(即在 AFE 上接收 JESD);这是否意味着 ADC 链路正在工作?

请帮助我们调试该问题。

提前感谢您、