尊敬的团队:

我们正在使用 FPGA、需要一些入门帮助。 如果您可以提供框架结构/K 代码任何其他材料、帮助我们了解连接板的要求、那很棒。

请查找 Latte 控制台上出现的错误

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Serdes-FIFO error for lane 0: 1

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Serdes-FIFO error for lane 1: 1

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 0; Alarms: 0x3300

###################################

###########Device DAC JESD-RX 1 Link Status###########

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

lane0 Errors=0b0111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error;

lane1 Errors=0b0000; Got errors:

lane2 Errors=0b0000; Got errors:

lane3 Errors=0b0000; Got errors:

CS State TX0: 0b00000000 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 1; Alarms: 0x700000000L

###################################

AFE Configuration Complete

#Done executing .. AFE7950/bringup/S5_OnboardClk_RX_TX_250M_10Gbps_4Lanes.py

#End Time 2023-12-11 14:51:45.469000

#Execution Time = 34.3320000172 s

#================ ERRORS:13, WARNINGS:1 ================#

我们需要理解以下几点

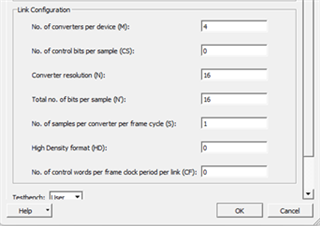

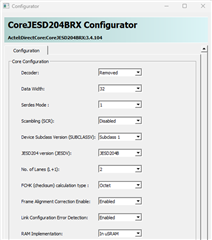

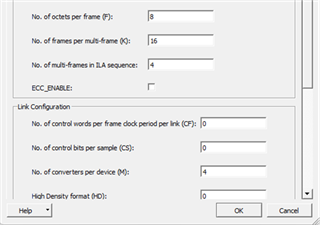

- 尽管它在所有通道中都显示错误、但我们使用的是24410 LMFS。

- 根据我们的理解、可能还有一些额外的帧、例如0b00001010或0b00000101、在开始时需要传输这些帧?

此致、

阿比谢克