您好!

我已将 AFE7900配置为 24410模式、能够在 RX 通道上接收数据。

我将在245.76MHz 采样频率上发送一个60kHz 的音调、并且能够在

汇编器[63:0]总线、但不在频谱分析仪中。

有什么建议吗?

--

此致

维韦克五世

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

e2e.ti.com/.../afe_5F00_config_5F00_log_5F00_DAC.txtHiDavid,

在启动期间、我没有收到任何 JESD 错误。

############################## GPIO ##############################

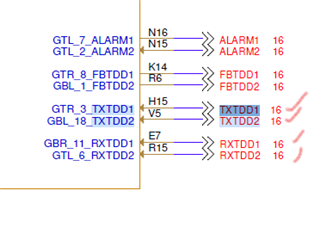

sysParams.gpioMapping ={

'H8':'ADC_SYNC0'、

'H7':'ADC_SYNC1'、

'N8':'ADC_SYNC2'、

'N7':'ADC_SYNC3'、

'h9':'DAC_SYNC0'、

'G9':'DAC_SYNC1'、

'n9':'DAC_SYNC2'、

'P9':'DAC_SYNC3'、

'P14':'GLOBAL_PDN'、

'K14':'FBABTDD'、

'R6':'FBCDTDD'、

'H15':['TXATDD'、'TXBTDD']、

'V5':['TXCTDD'、'TXDTDD']、

'E7':['RXATDD'、'RXBTDD']、

'R15':['RXCTDD'、'RXDTDD']}

"1-使用外部时钟时、没有用于检查时钟是否存在的寄存器。 要尝试将 DAC 设置为恒定测试模式。 这将意味着 DAC 将仅输出 NCO 频率、而无需来自 FPGA 的数据。 如果存在输出、那么我们就知道时钟正到达 AFE。 若要将 DAC 置于该模式、您可以在 Latte 中使用以下命令:

对于 I in [0、1]:

对于 j in [0,1]:

AFE.JESD.DACJESD[I].dacJesdConstantTestPatternValue (1,j,016384,0)# enable,channelNum,bandNum,ival,Qval

TXTTD1和 TXTDD2引脚被设为"高电平"。

在频谱分析仪的 TX 端口上仍然没有输出。

附加的日志

--

此致

维韦克五世

您好、Vivek、

在您的日志文件中、我注意到存在读检查错误。 您能否共享您正在使用的 spidwrites 文件、以便我们可以看到您遇到的确切错误?

由于 ADC 链路已接通、因此我不认为该问题与时钟有关。 其中一件事是探测并验证 TXTDD 引脚是否为"高电平"、以尽可能靠近 AFE。 如果 TXTDD 设置不正确、即使使用常量测试模式、也不会看到任何 TX 的输出。

要测试 TDD 引脚是否有问题、您也可以使用下面的 SPI 写入通过 SPI 覆盖 TDD 引脚。 应将这些写入添加到启动脚本的末尾。

dev_spi_write(0x15,0x80); dev_spi_write(0xec,0x1); dev_spi_write(0xf4,0x1); dev_spi_write(0xe4,0x1); dev_spi_write(0xed,0xf); dev_spi_write(0xf5,0x0); dev_spi_write(0xe5,0xf); dev_spi_write(0x15,00);

此致、

大卫·查帕罗

尊敬的 David:

我们将获取有关电阻器的以下读数。

R418 - 1.795V

R423 - 1.795V

和

我们观察到、当我们将 TX TDD 引脚的状态从1更改为0时、总电路板(PCB)电流值存在170mA 差异

TX TDD 状态"1"

1.114安

TX TDD 状态"0"

0.954A

为了隔离电路板(PCB)问题、我们将尝试多检查一个 PCB、由于需要组装 PCB、这可能需要一些时间。

同时、请告知我们是否可以读取或写入一些寄存器、以便我们可以确保不会出现配置问题。

--

此致

维韦克五世

尊敬的 David:

从上面的配置文件中、我无法在240MHz LO 获得 TXB 的任何输出。

如果 我的结论是配置不是问题的话。 这可能 是与硬件/原理图设计相关的问题。

请告诉我。

e2e.ti.com/.../afe_5F00_spi_5F00_log_5F00_30_5F00_ti.txt

--

此致

维韦克五世