工具与软件:

我们的设计在 可靠地初始化 TI FPGA IP 和 AFE7950之间的 JESDI 接口时遇到问题。 约50-60%的时间里、JESDI 接口的 ADC 侧无法可靠初始化。

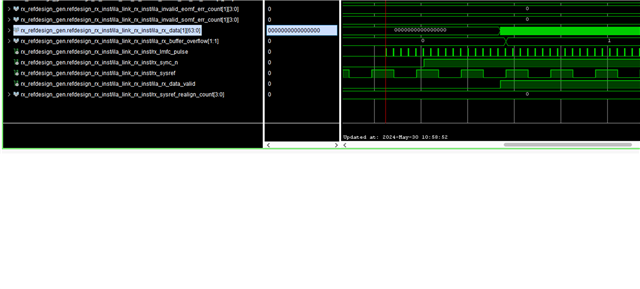

发生故障时、FPGA 中 ADC JESDI RX 接口上的信号会在包含的图像(第一个图像)中显示如下所示。

Rx_SYNC_RESET 在7950初始化时保持有效、但在 AFE 初始化和释放 Rx_SYNC_RESET 时、接收接口看起来不同步、也不会启动。

从下图可以看出 ILA_rx_data_valid 永远不会变为高电平、rx_sync_n 永远不会变为高电平。 不过可以看出、lmfc 脉冲序列恰好在 sysref 对齐计数从0变为1的点重新对齐。 此外、误差计数器中也为零错误。

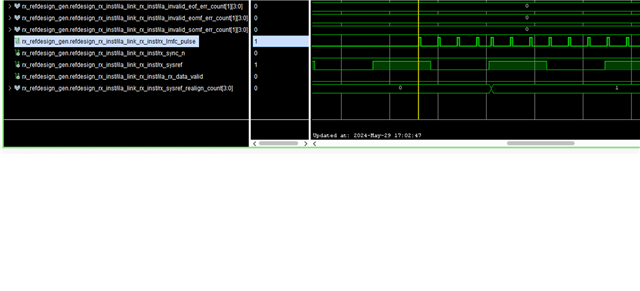

所包含的故障映像(第二个映像)是我们在初始化正确完成时看到的内容(见下文):

那么、我们如何诊断导致初始化失败的原因呢? 是否可以在 TI FPGA IP 内核的测试端口1、2、3上探测任何状态、这些状态可以让您对上述故障序列发生的原因有一定的了解?

IP JESDI 内核是否有更新?

谢谢

Joe