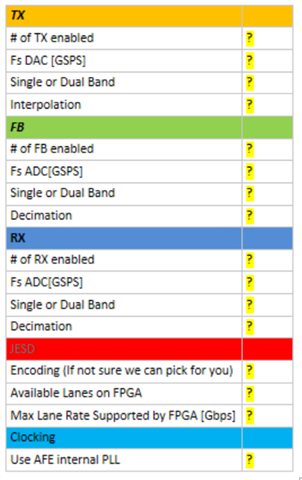

工具与软件:

在我们的项目中、我们计划使用 AFE7950器件、如下所示:

-使用4个 ADC 和4个 DAC ;

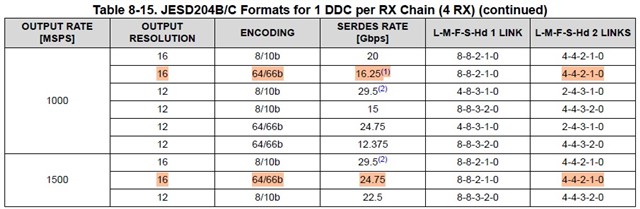

- 2个 ADC 输入信号将配置1000 MSPS 输出数据采样速率,

而其他2个需要配置为1500MSPS 输出速率;

-同样的配置将用于4个 DACs 的传输流程;

-我们的 FPGA 收发器的比特率限制为26 Gbps ;

-鉴于这两个要求,我们估算了两个情况下每个样本的最大位数(1000MSps 和1500MSps )。

AS (26位(13I+13Q)和16位(8I+8Q)):

13位 x 2 (Real (I)+ Imaginary (Q)) x 1GSPS = 26Gbps;

8位 x 2 (Real (I)+ Imaginary (Q)) x 1.5GSps = 24Gbps;

-我们的 ADC 必须配置1 DUC

问题:

如何使用这两个位数(13x2 (26b)和8x2 (16b))来配置 ADC 和 DAC? Latte 软件是否用于此用途?

2.如何将数据的 I 和 Q 部分组合成64b66b 格式(适用于 JESD204C)?