工具与软件:

您好!

我们使用的 AFE7921有一些问题。

过去,我们使用200m 带宽,我们的 AFE7921配置如下,我们的 sysref 为3.84MHz、JESD TX 和 JESD RX 速率为9.8304Gbps、它可以稳定地工作。

sysParams。 FRef = 245.76

sysParams。 FadcRx = 2949.1

sysParams。 Fdac = 2949.12*3.

sysParams.ddcFactorRx =[12、12、12]

sysParams.ducFactorTx =[36、36、36、36]

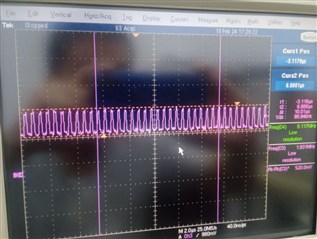

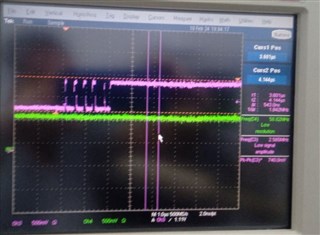

现在我们使用100M 带宽来节省 FPGA 资源和功耗、sysref 为3.84MHz、我们的 AFE7921配置如下所示、clk 和 adc/dac 速率相同、DDC 值加倍。 JESD TX 和 JESD RX 的速率为4.9152Gbps、但这种情况下不能稳定运行。有时链路断开、有时链路接通、然后链路断开切换。

sysParams。 FRef = 245.76

sysParams。 FadcRx = 2949.1

sysParams。 Fdac = 2949.12*3.

sysParams.ddcFactorRx =[24、24、24、24]

sysParams.ducFactorTx =[72、72、72、72、72]

我们还尝试更改 ADC/DAC 速率、AFE7921配置如下所示。 但这种现象是一样的,它也不是稳定的。有时链接断开,有时链接接通,然后链接断开切换。

sysParams。 FRef = 245.76

sysParams。 FadcRx = 1474.56

sysParams。 Fdac = 1474.56*3.

sysParams.ddcFactorRx =[12、12、12]

sysParams.ducFactorTx =[36、36、36、36]