Thread 中讨论的其他器件:AFE7950、

工具与软件:

大家好、团队!

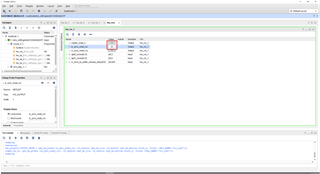

我们已经购买了 AFE7950评估板并将其配置为 ZCU102 FPGA。 为此、我们使用的是 TI 安全资源提供的.bit、.LTX 和 GUI 等资源。 最初按照 TI204c-Setup 文档中的说明配置 AFE。 编程后、如文档中所述、qpll0被锁定。

"为了设置 FPGA 以在 JESD 通道上发送 Tx 数据、我们首先需要执行以下步骤:

- 使主复位脱离复位状态(将 MASTER_RESET_n 设置为1)

- 当主复位为1时、qpllshould 锁定、由一个值3表示。

- 使 Tx 同步退出复位(将 TX_SYNC_RESET_VIO 设置为0)"

但经过几次下电上电后、当我们现在尝试对其进行配置时、在对 FPGA 进行编程后、qpll0不会被锁定、即 qpll0_locked 值不会更改。 两者之间没有修改任何代码。 但是、即使在多个电源循环中、电路板也配置不正确。

请帮助我们解决此问题!

谢谢你