工具与软件:

您好!

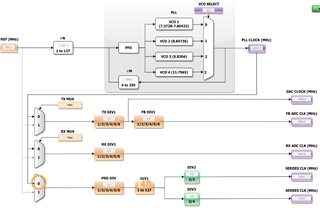

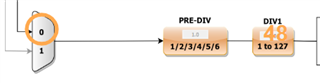

我已将 AFE7950器件安装在与 Xilinx FPGA 并置的 PCB 上、该 FPGA 对 TI_204C_IP_Ref.sv 设计进行实例化。 我之前在 AFE7950EVM 评估平台上实例化了相同的设计、该平台提供491.52 MHz REFCLK。 在我们的设计中、我们在500 MHz 处驱动 REFCLK。 我们直接从 PLL 提供该时钟、因为我们最终会直接将12000 MHz 作为采样时钟提供给 DAC。 我们的启动方法是:

1.在 Latte 中运行附带的脚本 setup_500.00_ddc48_fb24_duc96_DB.py、通过 SPI 配置 AFE7950EVM

2.从 Latte 终端捕获 SPI 序列

3.在我们的定制 PCB 系统上执行从采集序列中执行的所有 SPI 写入和读取操作

4.捕获 500.00_ddc48_fb24_duc96.log、其中显示了我们的定制 PCB 设置中的所有 SPI 事务

我假设日志中的以下序列告诉我 PLL 未锁定:

Writing into 0x0066 value 0x00 Writing into 0x0066 value 0x01 Writing into 0x0066 value 0x03 Writing into 0x0063 value 0x41 Writing into 0x0063 value 0x01 Reading From 0x0066 value 0x03 Reading From 0x0066 value 0x03 Reading From 0x0066 value 0x03 Reading From 0x0066 value 0x03 Writing into 0x0066 value 0x31

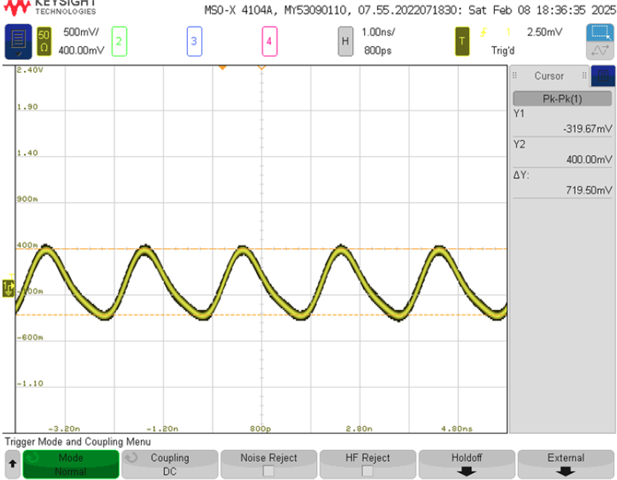

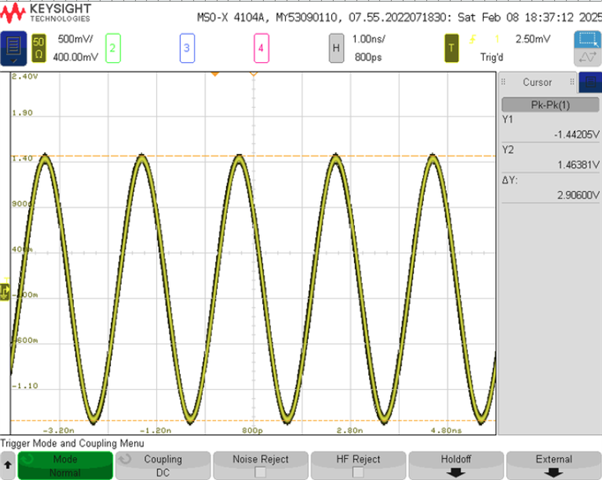

我捕获了一些示波器捕获来调查 REFCLK 的行为:

带有高阻抗探头的 REFCLK+:

带高阻抗探头的 REFCLK-:

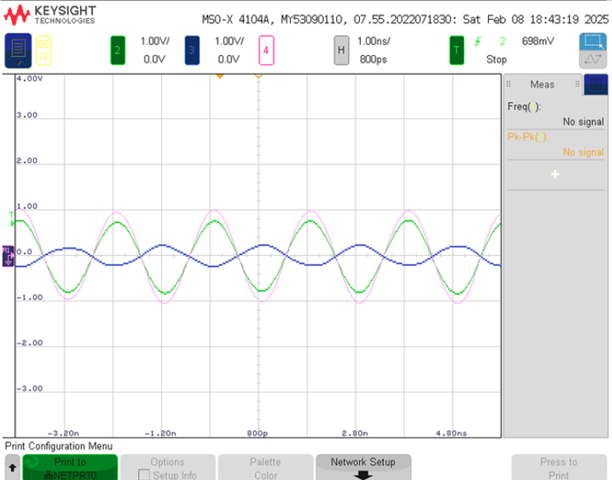

具有低阻抗探头的 REFLK +/-和差分探头:

我已经将 REFCLK 频率测量为500 MHz。 我注意到+和-腿之间的不平衡。 我还注意到、2V 摆幅(差分)略高于1.8V Vppdiff 的建议运行条件。

您是否认为降低差动摆幅的幅度是正确的做法? 您还可以看看我的脚本和日志、看看脚本是否看起来正确、以及日志中是否还有其他任何内容指示不同的问题?

谢谢!

Jesse