工具与软件:

专家们、您好!

我在构建 PCB 设计、想知道 PCB 的最低要求。

我甚至不需要像 LVDS 一样的跟踪、我只需要 UART 连接(当然、PCB 将根据 swr166 / sprr418 -只需要部件 )

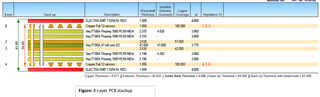

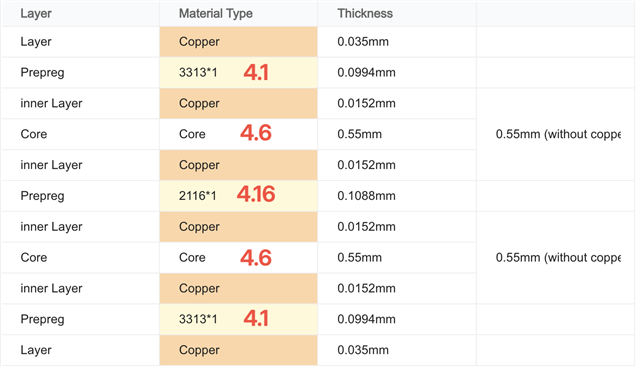

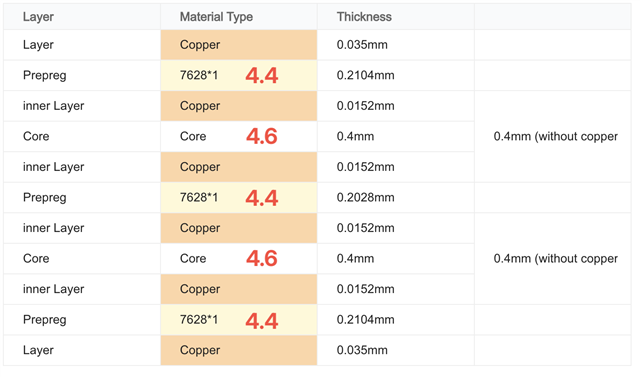

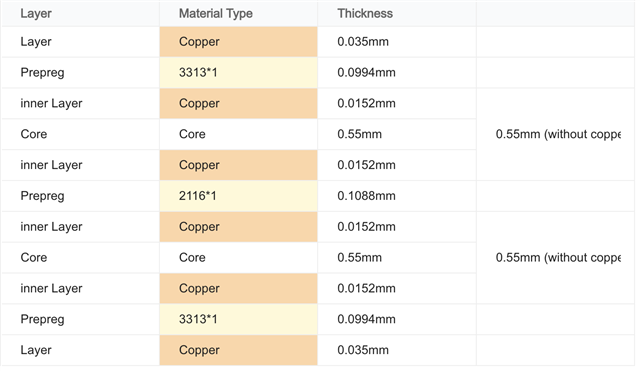

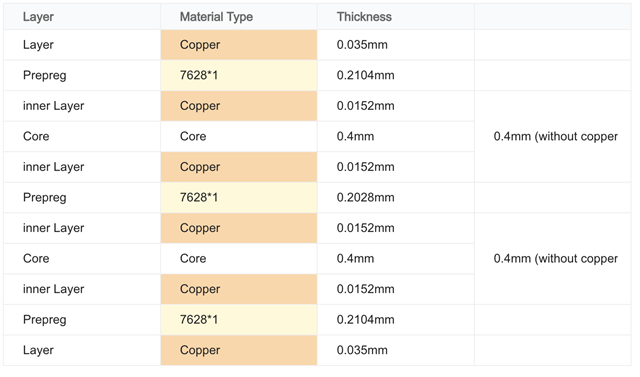

我已经读取了 Up_Schematic_ Layout_Checklist 上提供的 PCB 堆栈。

文档和论坛上的一般信息是使用建议的堆叠来避免性能下降。

但是、我认为 AOP 的重点是放宽 PCB 要求、因为 天线是封装天线。

我想知道在不 降低性能的情况下、用于原型设计/初始小规模制造的最低要求是什么。

我不知道该怎么说。"

以下任何一项对于简化版本的参考设计是否足够?

提前感谢您的帮助。