主题中讨论的其他器件: AWR1642、 AWR1443

尊敬的团队

希望您能帮助我的客户、请查看以下查询。

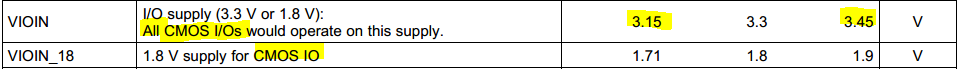

1) 1)数据表给出了以下有关 VIOIN 的信息:

最大/最小值仅与3.3V 匹配。 那么、我可以为 VIOIN 使用1.8V 电压吗? 在这种情况下、限制是多少(最小值/最大值)?

VIOIN_18的用途是什么? VIOIN 用于为所有 CMOS I/O 供电。 您可以澄清这个问题吗?

2) 2) 有两个射频电源:VIN_13RF1和 VIN_13RF2、在旁路模式下可由1.3V 或1V 供电。 在使用1V 电源时、AWR 如何知道绕过其内部 LDO? 如果是旁路、我是否应该将电容器连接到 VOUT_PA?

3) 3) 从单独的外部 LDO 提供 VIN_13RF1和 VIN_13RF2是否有一些优势? 这些电源是否共享相同/不同的 LDO? 有一个表5-3表示1.3V 耗电元件消耗的电流为2A。 您能否告知此电流在 VIN_13RF1和 VIN_13RF2之间的分布(如果它们可以单独提供)?

4) 4) 您是否知道每个1.8V 电源的电流消耗? 我是否应该分别为模拟用户(如合成器、APLL、VCO 等)和数字1.8V 用户(如 VIOIN_18DIFF)提供安静的1.8V 电压?

5) 5) 如果我要在每次上电/复位时通过 SPI 上载器件的固件补丁、我是否可以省略使用 QSPI 闪存? 如果可以、我是否应该将未使用的 QSPI 引脚连接到上拉/下拉? 顺便说一下,从表3-1可以看出 AWR1243没有 QSPI… 是真的吗?

6) 6) 您是否计划删除 LVDS 模式? 为什么在表3-1中将其称为 LVDS/Debug?

7) 7)表3-1显示 AWR1243没有 GP ADC。 但是、根据表4-1、有6个 GPADC 引脚。 什么是真的?

8) 根据 AWR1243勘误表(SWRZ071–2017年5月)、CSI 接口和射频 TX (ANA#07)之间存在一些串扰。 您是否知道 TI 是否计划修复此错误? 如果是、它是否会影响引脚?

如果您能回答上述问题、我将不胜感激。

提前感谢

BR

Shai