请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:IWRL1432 工具与软件:

您好、

客户有关于器件时钟的以下问题。 您可以帮助吗?

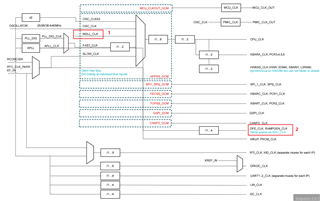

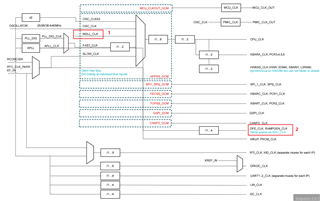

MDLL_CLK 的时钟源是什么? MDLL_CLK 的频率是多少? 它是如何生成的?

DFE_CLK、RAMPGEN_CLK、ADC_CLK 的时钟源是什么? 是 APLL 吗?

谢谢!

Chris

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、

客户有关于器件时钟的以下问题。 您可以帮助吗?

MDLL_CLK 的时钟源是什么? MDLL_CLK 的频率是多少? 它是如何生成的?

DFE_CLK、RAMPGEN_CLK、ADC_CLK 的时钟源是什么? 是 APLL 吗?

谢谢!

Chris

Ankit、

您可以在 TRM 中找到它。 https://www.ti.com/lit/pdf/swru599

谢谢!

Chris