Other Parts Discussed in Thread: TPA3136D2

工具/软件:

您好:

我正在使用 TPA3136D2 、想澄清一个有关其输出削波期间的占空比行为的问题。

根据数据表:

9.1 概述

“这些电容器确保即使在低频音频信号削波期间也能充分储存能量、从而使高侧功率级 FET (LDMOS) 在其导通周期的剩余部分完全导通。“

9.3.3 PLIMIT

PLIMIT 电路对输出峰峰值电压进行限制。 通过将占空比限制为固定的最大值来实现限制。 该限值可视为低于连接到 PVCC 的电源的“虚拟“电压轨。 “虚拟“电源轨大约是 PLIMIT 引脚电压的四倍。 输出电压可用于计算给定最大输入电压和扬声器阻抗下的最大输出功率。

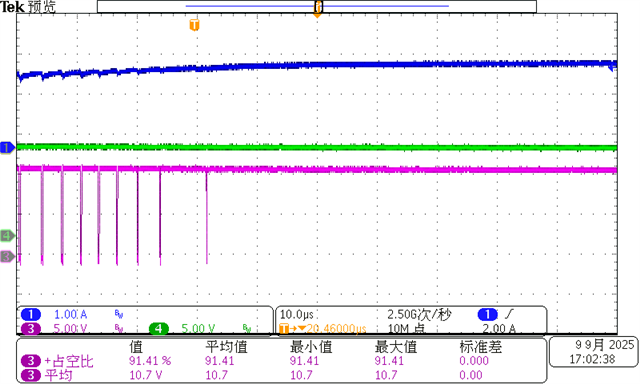

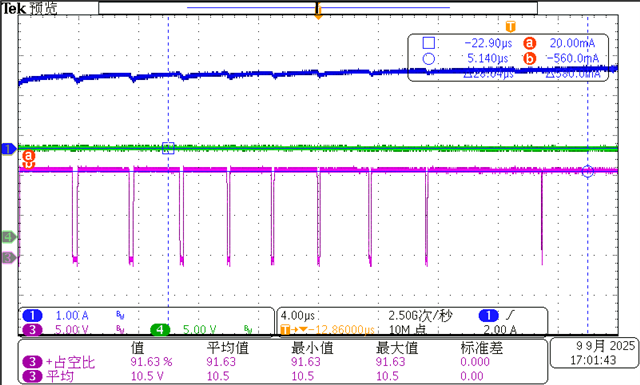

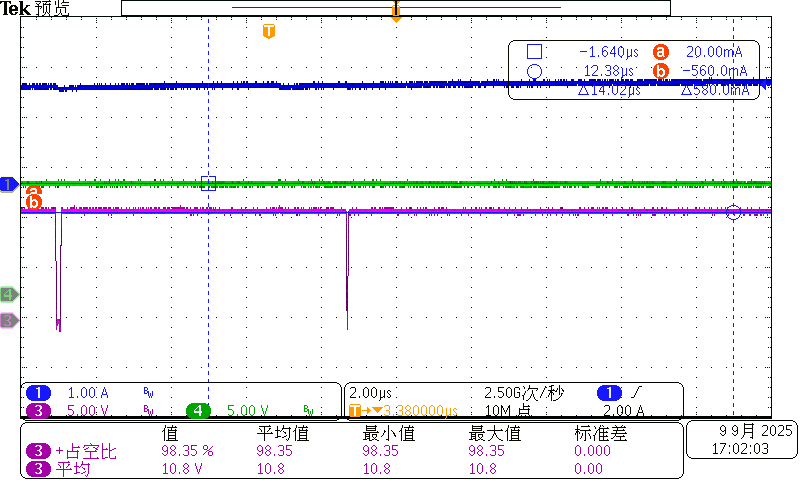

根据我的测量结果、在削波期间、OUTNL/OUTNR 占空比似乎可以达到 100%。 我想确认该 IC 是否确实能够实现完整的 100%占空比。

我的电路配置如下:

-

AVCC = 12V

-

RL = 4Ω

-

PLIMIT = 1/2 * GVDD

-

BTL 模式=单通道 PBTL 模式

- 扬声器输出功率≈3W

随附了三个波形屏幕截图、显示了削波期间占空比接近 100%。 任何人都可以确认我的观察结果是否正确、或者此配置中是否存在我可能忽略的问题?

提前感谢您的见解!