Other Parts Discussed in Thread: USB-TO-GPIO2

器件型号: USB-TO-GPIO2

您好、

抱歉!! 我不确定此查询适用于哪个论坛。 请考虑或将其移至相关论坛。

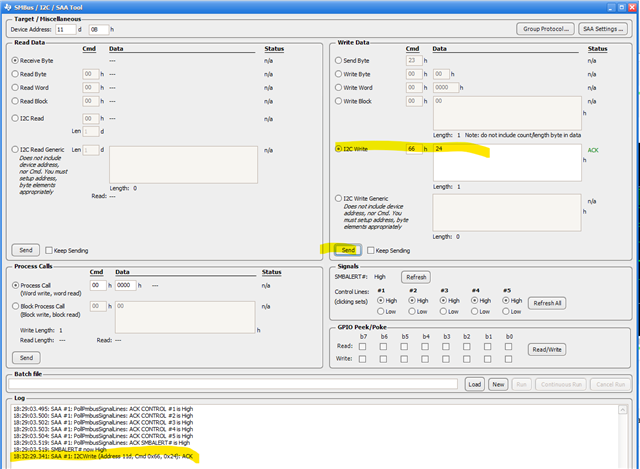

我正在使用 USB-TO-GPIO2 与 Fusion Digital Power Design 工具。 我仅使用总线连接器的引脚 9 和 10 来连接具有 I2C 线路的 FPGA。 我认为时钟频率将为 400kHz、如下所示:

当我通过在 GUI 中选择 I2C 进行写入操作来发送数据和命令时、我看到通过 JTAG 电缆连接的 FPGA 板的 2 行 ILA 上的数据如下所示:

那么、器件的这种预期行为是什么? 为什么当我仅发送一次时、这个 SCL 和 SDA 信号会持续切换? 而且接收到的数据也不匹配、为什么?

我只是在 RTL 中首先读取地址、如果匹配、然后读取下一个数据。 我有什么遗漏吗? 请帮助我了解有关此器件的更多信息。

此致