主题中讨论的其他部件:ISO6721, ISO7721, ISO6721-Q1,

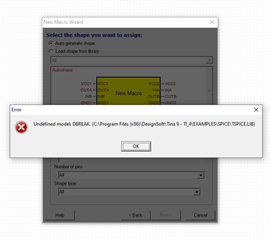

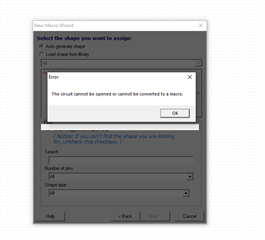

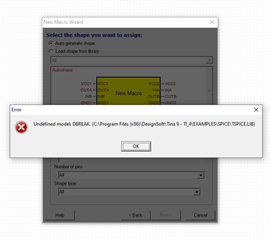

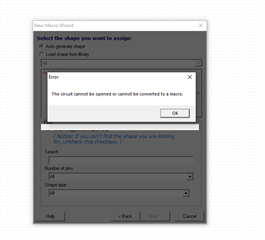

我试图 通过宏向导工具将ISO6721和ISO7721 Spice模型插入到TINA中,但我收到以下DBREAK错误。

请就此提供帮助。 提前感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我试图 通过宏向导工具将ISO6721和ISO7721 Spice模型插入到TINA中,但我收到以下DBREAK错误。

请就此提供帮助。 提前感谢!

* ISO6721

*****************

*(C)版权所有2019 Texas Instruments Incorporated。 保留所有权利。

*****************

**此模型设计用于帮助德州仪器(TI)的客户。

** TI及其许可方和供应商不作任何明示的保证

**或暗示,包括的保证

**适销性或对某一特定目的的适用性。 型号是

**完全按"原样"提供。 质量的全部风险

**性能与客户有关

*****************

*

*此型号如有更改,恕不另行通知。 德州仪器(TI)

*公司不负责更新此模型。

*

*****************

*

*发布人:德州仪器(TI)

*部件:ISO6721/ISO6721-Q1</s>6721

日期:2021年5月28日

*型号类型:瞬态

*模拟器:PSpice

*模拟器版本:17.4 2021 (x64)

*数据表:SLLSFJ0C–2020年1月–2021年5月修订

*

*型号版本:1.00

*

*****************

*************

*宏模型模拟参数:

*************

*电源UVLO+/-

*输入VIH/VIL

*输入电容

*输出上升/下降时间

*禁用时输出高阻抗

*传播延迟

*未对高电压性能进行建模

******

SUBCKT ISO6721 VCC1输出INB GND1 VCC2 INA OUTB GND2

XU1 VCC1 GND1 1 2 VCC1_INT POWER

XU2 VCC2 GND2 3 4 VCC2_INT POWER

XU3 INA DEL_INA 5 6 VCC2_INT GND2 7输入

XU4 DEL_INA DEL_OUA 8延迟

XU5 VCC1 DEL_OUA VCC1_INT GND1 OUA 9 10输出

XU6 INB DEL_INB 11 12 VCC1_INT GND1 13输入

XU7 DEL_INB DEL_OUTB 14延迟

XU8 VCC2 DEL_OUTB VCC2_INT GND2 OUTB 15 16输出

结束

SUBCKT输入输入输出INB_INT INT INT VCC VSS Thres

E_ABM21输出0值{ IF(V(INT)> 0.51 ,5,0)}

E_E20 INB_INT 0 N1676.6925万 VSS 1

R_R10 N1676.6925万 in 985 TC=0,0

E_ABM3 INT 0值{ IF ( V(INB_INT)> V(Thres),1,0)}

VCC断路器中的D_U1

D_U2 VSS处于中断状态

R_R11 VCC N1.67669251亿.5MEG TC=0,0

E_ABM22 Thres 0 value { IF ( V(INT)< 0.5 ,0.7 ,0.3 )}

C_C1 VSS N1676.6925万 2.8p TC=0,0

结束

SUBCKT POWER VCC VSS VCC_INT2 HYST VCC_OUT

E_ABM1 VCC_INT2 0值{ IF ( V(VCC_INT)> V(HYST), 1,0)}

V_V1 N1676.9409万 0 1.53

E_E1 HYST N1676.9409万 VCC_INT2 0 - 0.13

E_E21 VCC_INT 0 VCC VSS 1

E_ABM2 VCC_OUT 0值{ IF ( V(VCC_INT2)> 0.5 ,V(VCC),0)}

结束

SUBCKT DELAY IN_DEL OUT IN_OK

R_R5 0 IN_OK 1K TC=0,0

E_E8输出_交货0输入_确定01

T_T2 IN_DEL 0 IN_OK 0 Z0=1K TD=9.5n

结束

SUBCKT输出EN输入VCC VSS输出Topa Bota

E_ABM6 DRVB 0值{ IF (V (N1677.4625万)>(V (VCC)-V (VSS))/2+V (VSS),V (输入),-10)}

R_R45 N1677.1405万 VCC 50 TC=0,0

R_R51 N1677.1631万输出50 TC=0,0

X_S2 Bota 0 N1677.1631万 VSS SCHEMATIC3_S2

X_S1 Topa 0 N1677.1405万输出SCHEMATIC3_S1

E_ABM7 Topa 0值{ IF ( V(DRVB)> 2.5 ,1,0)}

E_ABM8 N1677.7893万 0值{ IF ( V(DRVB) 2.45 & V(DRVB)>-5,1,0 )}

D_U1输出VCC断开

D_U4 VSS EN断点

D_U2 VSS输出断路器

R_R11 VCC N1677.4625万 2MEG TC=0,0

D_U3 EN VCC断点

R_R10 N1677.4625万 EN 1970 TC=0,0

C_C1 VSS OUT 7.58331305896909E-12 TC=0,0

R_R52 N1677.6225万 N1677.6248万 5MEG TC=0,0

C_C2 N1677.6248万 VSS 1f TC=0,0

E_ABM9 HIHI 0值{ IF ( V(DRVB)<-5,1,0)}

X_S3 HIGHI 0 N1677.1631万 N1677.6225万 SCHEMATIC3_S3

R_R54 N1677.7893万 Bota 1 TC=0,0

C_C3 0 Bota 8.68588963806504E-11 TC=0,0

结束

subckt SCHEMATIC3_S2 1 2 3 4

S_S2 3 4 1 2 _S2

RS_S2 1 2 1G

model _S2 vSwitch roff=5e6 0.01 voff=0.8V Von = 1.0V

结束SCHEMATIC3_S2

subckt SCHEMATIC3_S1 1 2 3 4

S_S1 3 4 1 2 _S1

RS_S1 1 2 1G

model _S1 vSwitch roff=5e6 0.01 voff=0.0V Von = 1.0V

结束SCHEMATIC3_S1

subckt SCHEMATIC3_S3 1 2 3 4

S_S3 3 4 1 2 _S3

RS_S3 1 2 1G

model _s3 vswitch roff=5e6 ron=voff=0.0V 0.01 von = 1.0V

结束SCHEMATIC3_S3

您好,GP,

错误是指未定义的型号“DBREAK”,它是PSpice中的内置二极管。

简而言之,此模型不能按当前状态导入TINA-TI,我们建议您尝试在PSpice for TI中使用此模型进行仿真,该模型可从以下网址下载: https://www.ti.com/tool/PSPICE-FOR-TI

如果您有任何其他问题,请告知我们。

谢谢!

Manuel Chavez