主题中讨论的其他器件:TINA-TI、

工具/软件:TINA-TI 或 Spice 模型

您好!

我正在使用 TI 提供的 ibis 模型在 HyperLynx 2.4中模拟 USB1数据信号。

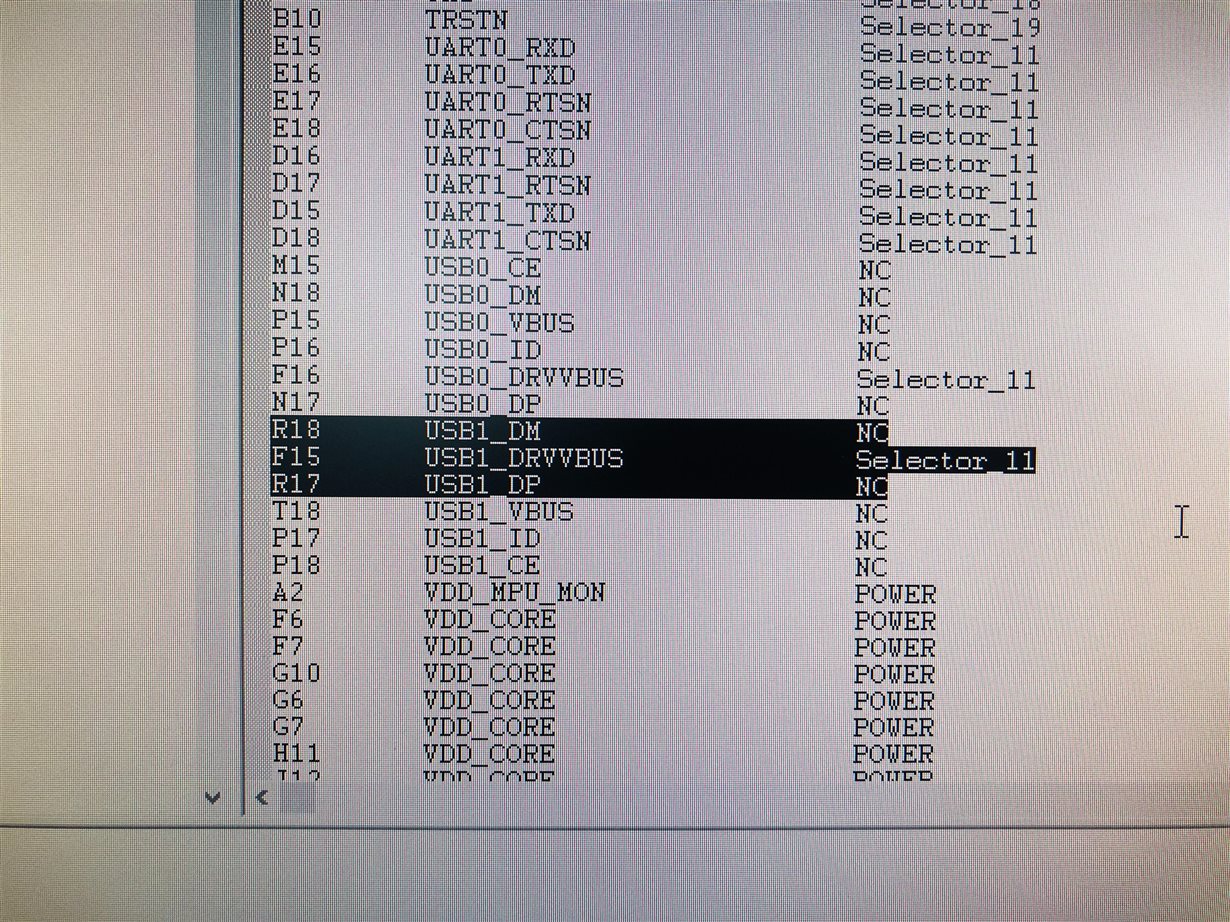

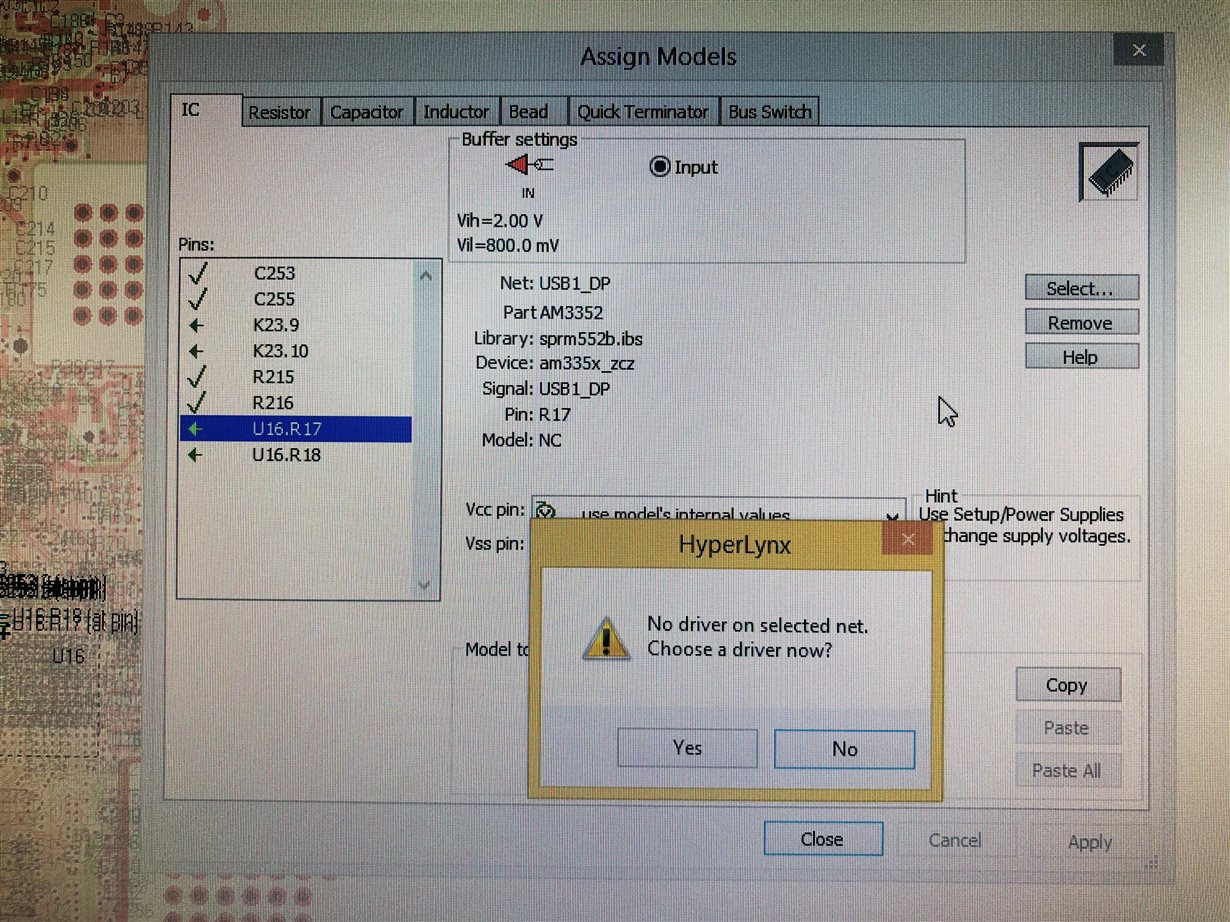

对于 USB1、在 ibis 模型中将数据信号模型定义为 NC、 因此、在分配模型时、我无法选择它作为输出(请参阅下图)。由于它是数据信号、我可以将任何连接的 IC 定义为输出驱动器、但我的问题是信号通过具有 ESD 保护的共模滤波器、因为我已经为其分配了 S 参数 也定义为仅输入的连接器。

因此、在仿真时、我会得到未选择输出驱动器的误差。

我曾尝试通过将模型更改为选择器来更改 ibis 模型、但在这种情况 下、虽然允许我将其定义为输出、但我会根据选择器上拉定义(1.5V 或1.8V 或3.3V)获得输出、而不是预期(400mV)信号。

建议我如何将 AM3352的 R17和 R18引脚定义为 I/O,或者我应该选择哪个选择器,因为所有选择器都定义了上拉电阻? 请为定义为 I/O 的这两个引脚发送更新的 ibis 模型