请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:Tina-TI 工具/软件:TINA-TI 或 Spice 模型

我正在尝试对 TINA-TI 中的全桥电源转换器进行建模、并需要隔离晶体管栅极。 从 Vishay 6N137和 Spice 模型中找到了合适的光耦合器。 以下是模型列表:

(二 * 10MBd 高速光耦合器6N137库 *版权所有 Vishay、Inc. 2016保留所有权利。 (二 (二 ** Vishay 光耦合器的 PSpice 模型 **高速10 MBd ** 6N137、VO2601/2611、VO2630/2631、VO4661 (二 **使能端高电平、NMOS 输出 **-- 6N137、VO2601/2611 -- -- ** **模型节点-符号-引脚 ** 1 (DA) A 2**2 (DK) k 3** 3 (GND) GND 5** 4(Vo) Vo 6** 5(VE) Ve 7**6 (VCC) VCC 8** *$ .SUBCKT 6N137 DA DK VO VE VCC DD1 DA 6 demit vV1 6 DK DC 0 WW1 VCC 7 vV1 I_SW1 RR3 GND 7 1K xU2 7 VE 8 $G_DPWR $G_DGND 和2 RR4 8 9 5K RR5 VCC 100K MQ1 VO 9 GND MOST1 GND W=9.7M L=2U;NMOS 输出 .model demit D +IS=1.69341E-12 RS=2.5 N=2.4 XTI=4 +EG=1.52436 CJO=1.80001E-11 VJ=0.75 M=0.5 .MOST1 KP NMOS (level=3=25U VTO=2RD=45) *ISO=0.20Rd=1 Rd=1 ron.I=1.20nS (2.5N **双通道 NMOS 输出 **-- VO2630/2631、VO4661 -- -- ** **模型节点-符号-引脚 ** 1 (A1) A1 1 ** 2 (K1) C1 2 ** 3 (K2) C2 3** 4(A2) 答2. 4** 5 (GND) GND 5** 6(VO2) 二氧化碳 6** 7(VO1) VO1 7**8 (VCC) VCC 8** .SUBCKT VO2630 A1 K1 K2 A2 GND VO1 VCC **通道1 ** DD1 A1 61 demit vV1 61 K1 DC 0 WW1 VCC 71 vV1 I_SW1 rR13 71 GND 1K xU11 71 81美元 G_DPWR $G_DGND BUF rR41 81 91 5K MQ11 VO1 91 GND MOST1 W=9.7M L=2U;NMOS 输出 **通道2 ** DD2 A2 62 demit vV2 62 K2 DC 0 WW2 VCC 72 vV2 I_SW1 rR23 72 GND 1K xU12 72 CJ82 $G_DPWR $G_DGND BUF rR24 82 5K MQ1 VO2 92 GND MOST1 W=9.7M L=2U;NMOS 输出 ** .model demit D +is =1.69=1.752M=0.5=1.45M =1.75M =1.45M MOST1 L =0.5M =0.5M =0.5M =0.5M =1.45M =0.5M =1.45M =1.24M =1.24M =1.24E 模型 Nmos (level=3 KP=25U VTO=2 RD=45) .model I_SW1 ISWITCH (roff=1e6 Ron=1 IT=4.9m Ih=0.1m Td=20ns) .ends *$**$***--- **-1输入缓冲 器**.SUBCKT BUF I0 O 可选:DPWWR=$G_DPWR DGND=$G_DGND U1 BUF DPWR DGND I0 O + D_PLD_GATE IO_PLD .END *$***--- **.1输入逆变 器**.SUBCKT INV I0 O 可选:DPWR=$G_DPWR DGND=$G_DGND * U1 INV DPWR DGND I0 O + D_PLD_GATE IO_PLD * .END *$***--- **启用具有三态输出 的高缓冲器** .SUBCKT BUFTH I0 OE O 可选:DPWWWW=$G_DPWR DGND=$G_DGND U1 BUF3 DPWR DGND I0 OE O + D_PLD_TGATE IO_PLD .END *$***--- **启用具有三态输出 的低缓冲器** .SUBCKT BUFTL I0 OE O 可选:DPWWR =$G_DPWR DGND=$G_DGND U1 INV DPWR DGND OE OEBAR + D_PLD_GATE IO_PLD * U2 BUF3 DPWR DOEI0$ BAR O + D_PLD_GPOS--- *2输入与门 *.SUBCKT 和2 I0 I1 O 可选:DPWWR=$G_DPWR DGNDGND=$G_DGND U1和(2) DPWR DGND I0 I1 O D_PLD_GATE IO_PLD .END *$ *--- 模型 D_PLD_GATE UGATE *$ .MODEL D_PLD_TGATE UTGATE *$ .MODEL D_PLD_EFF UEFF *$ .MODEL D_PLD_GFF UGFF *$ .MODEL IO_PLD UIO *$==================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================== * *注意: * * Al经久 耐用的型号可作为评估器件的有用工具 * **性能、它们无法对确切的器件性能建模 * **在所有条件下、它们也不是要替换的 * *实验电路板以进行最终验证! * * * * Vishay Semiconductors GmbH 提供的模型不是 * *完全表示所有规格和运行情况 * *半导体产品的特性 * *模型相关。 * *模型描述了典型器件的特性。 * **在所有情况下、给定的当前数据表信息 * **器件是最终设计指南、也是唯一的实际设计指南 * *性能规范。 * * Vishay Semiconductors 不承担由此产生的任何责任 * *。 Vishay Semiconductors 保留* *更改模型的权利、恕不另行通知。*================================================================================================================================ *

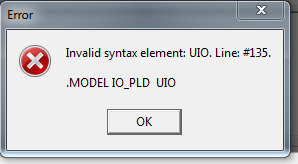

当我在 TINA-TI 中为此光耦创建宏时、我会遇到错误

很明显、问题出在 UIO 状态中、即 PSpice 指令。 TINA-TI 是否支持此指令? 如果不是、我可以使用其他产品进行更换吗?