工具/软件:WEBENCH设计工具

您好!

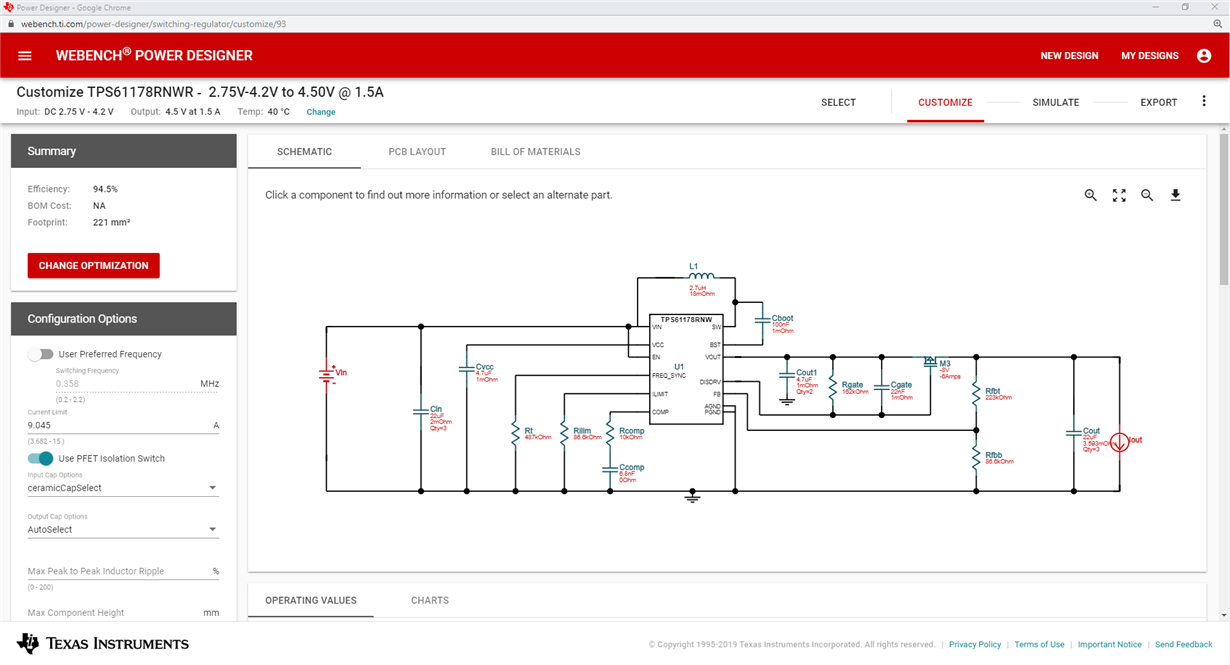

我将在我的设计中使用 TPS61178。 我之所以选择该器件、是因为它支持输出过压和短路保护。 我是由 Webench 设计的、具有以下参数:

VIN=2.75V 至4.2V

Vout= 4.4V

Iout=1.5A

温度=40

https://webench.ti.com/power-designer/switching-regulator/customize/93

我获得了采用推荐的 Vishay SI5499DC 外部 P 沟道 FET 的设计。

SI5499DC 的最大 Vgs 为5V。 但 Webench 计算出的 Rgate 为162K。

TPS61178数据表中的公式显示:

Vgate =栅极* IDIS_PFET

Vgate = 162K * 55uA

Vgate=8.91V、远高于 FET SI5499DC 的 Vgs 绝对最大值。

1. Webench 计算出的 Rgate 是否正确、或者我不了解什么?

2. SI5499DC 的 Vgs 和 Vds 最大值分别为5V 和8V。 这意味着、通过使用此 FET、本设计将不会满足 TPS61178的23V 输出电压绝对最大值(当有人将23V 的电压连接到输出时)。 我是对的吗?

随附的原理图图像:

此致、

Ramin