请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS50601-SP 工具/软件:WEBENCH设计工具

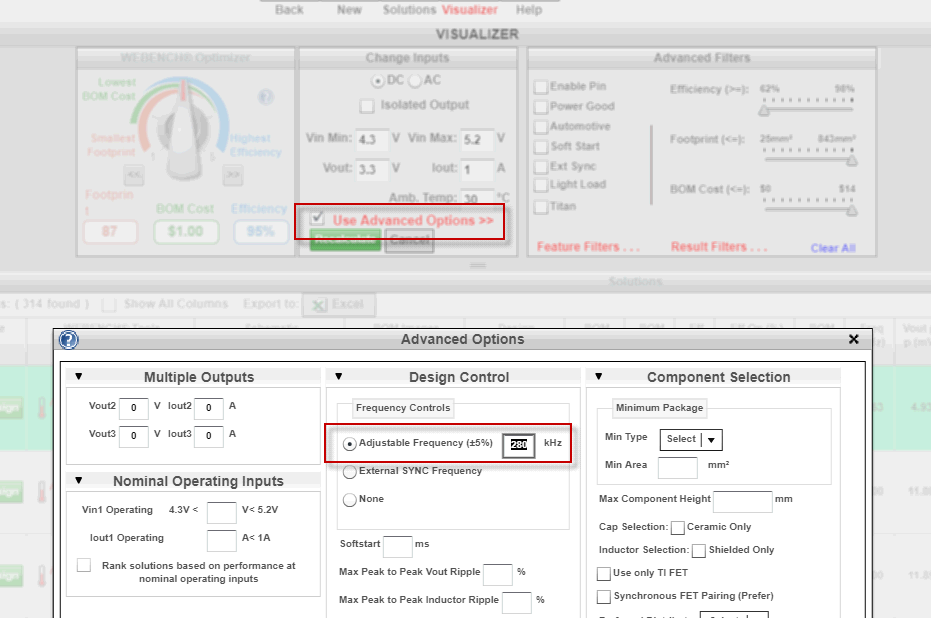

我正在尝试使用以下设计输入为 TPS50601-SP 创建 Webench 设计:VIN = 4.3至5.5V、Vout = 3.3V、Iout = 1A。

Webench 报告无法创建设计、给出的原因是"计算出的占空比大于关闭时间导致的占空比"。 这是没有道理的。 如果我将最大 Vin 电压降低到5.2V 或5.0V、则该设计工作正常。 使用这些较低的 Vin 设置时、占空比实际上更高。 该器件似乎应该能够在输入电压= 5.5和输出电压= 3.3V (Fsw 大约为390KHz)的条件下运行。 如果需要、低侧 Vin 会由于高占空比而推送最小关断时间限制。

此设计输入是否违反了其他一些设计参数?