Other Parts Discussed in Thread: PMP10352, CSD18504Q5A

主题中讨论的其他器件: CSD18504Q5A

您好!

我是来自 Magnetika 的 Guillermo Durà ó n。

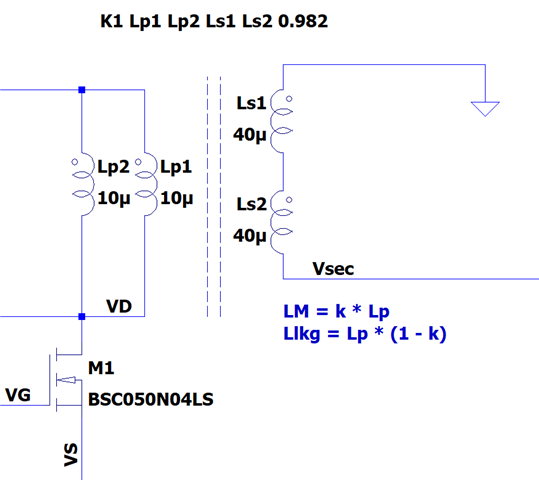

我们正在尝试创建我们自己的具有利兹线和 E 芯的变压器。 此时、作为第一个原型、我们将使用您的 PMP10352隔离反激式转换器作为基准。

因此、我们采用正确的焊盘连接变压器的端子。 目前、我们只执行一个和两个绕组、因为它更容易。

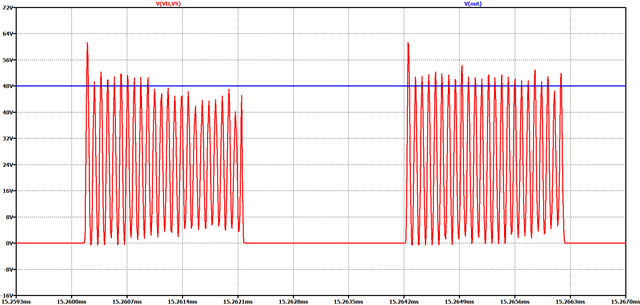

在仿真中、我们可以看到每当变压器出现泄漏时、FET 的 VDS 信号中都会出现大量振铃、参考设计中使用的变压器的额定电压为40 VDS、因此、我认为它可能会被烧毁。 我有两个关于此参考设计的问题。

实际变压器中是否存在所用脉冲的漏电感? 这个多少钱?

在实践中、通过 FET 的电流和电压中是否产生过大量的振铃?