Other Parts Discussed in Thread: PMP11329, LM5021, UC3844

主题中讨论的其他器件: LM5021、 UC3844

您好!

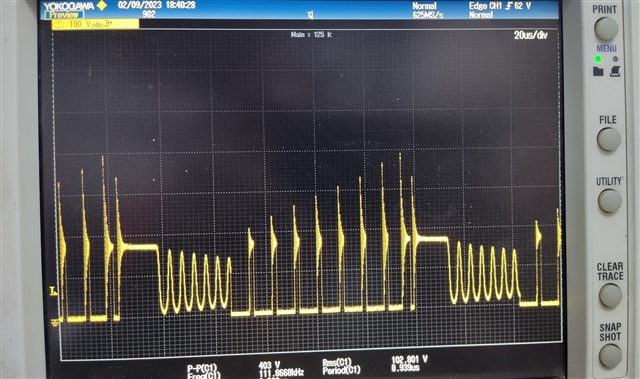

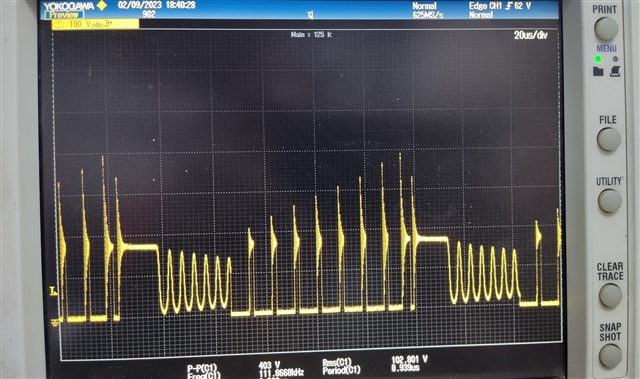

我正在将 TI 参考 设计 PMP11329用于我的一个输出为18V、3.6A 的电源设计。 我能够获得2A 的输出、但漏极波形或整个环路会振荡。 漏极波形如下所示。 开关频率当前为100kHz。 最初我还尝试使用150kHz。

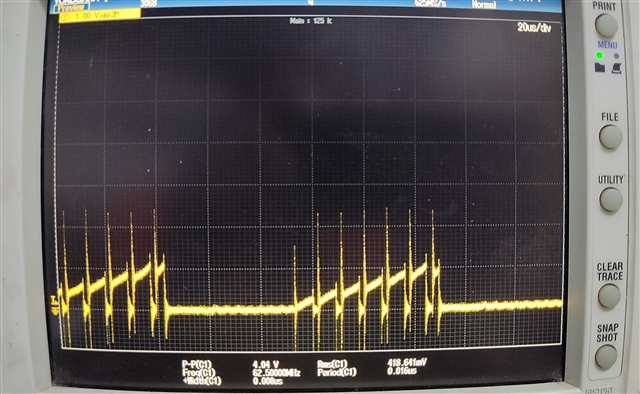

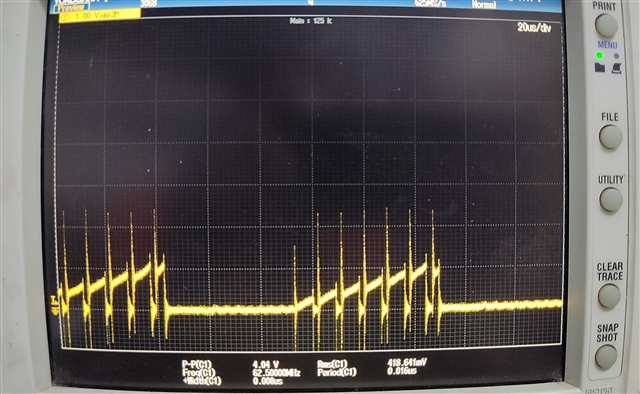

电流检测波形如下所示、其中采用500m Ω 检测电阻。

请帮我解决这个问题。 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: PMP11329, LM5021, UC3844

您好!

我正在将 TI 参考 设计 PMP11329用于我的一个输出为18V、3.6A 的电源设计。 我能够获得2A 的输出、但漏极波形或整个环路会振荡。 漏极波形如下所示。 开关频率当前为100kHz。 最初我还尝试使用150kHz。

电流检测波形如下所示、其中采用500m Ω 检测电阻。

请帮我解决这个问题。 谢谢。

CS 布线跨接在电路板上并不理想、但这似乎是布线该部分并将 FET 设置在 PCB 底部边缘的唯一方法。

CS 布线看起来不错、将其布置在接地平面旁边是尽可能减小环路电感的好方法。 我认为您唯一可以更改的是控制器的滤波。

如果我正确读取了布局、看起来 CCS 会经过两个过孔、然后返回 LM5021的 GND 引脚。 这种额外的电感可能足以让噪声跳闸 OCP。 在 PCB 中、您是否可以翻转电容以使接地连接直接连接到 LM5021的 GND 引脚? 下面的示意图展示了在哪些方面可以做到这一点。

过孔还可用作天线并拾取噪声、因此有助于尽可能减少敏感节点上的此类数量。

此外、这里还有一个链接、指向我认为有用的文章、它介绍了设计布局时的各种注意事项。