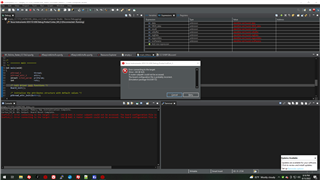

我开发了一个定制板、将 CC1310F128RGZ 和 CC1312用作调试器和编程器。 我正在使用"empty"项目执行一些初始测试、但我遇到了一个问题、即代码似乎仅在调试模式下运行、并通过具有断点的代码手动步进(F6)。 如果我移除断点并继续调试、代码将不会运行。 即使退出调试、代码看起来也不会运行。

我已将 LF XTAL 设置为#define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x3// LF RCOSC、这似乎不能解决问题。

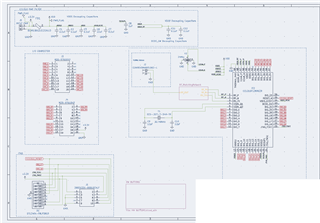

此外、我的定制电路板还参考 C1310 LP 原理图和 PCB 设计指南进行构建。 下面是定制板的原理图