您好、TI 团队:

我遇到了数据包丢失 和相关的低 RSSI 的问题、但这个问题只用于更长的(例如、1400字节)传输。

我们以915.25MHz、750ksym/s 4-FSK 运行、PHY 设置如下:

// 1.5Mbps // See SVS's post here for these trusted, official settings: // e2e.ti.com/.../2363574 const rfc_CMD_PROP_RADIO_DIV_SETUP_t Cc1310_Rf900vol_PHY_900M_750KSYM_4fsk_g = { // Use Smart RF Studio to generate rxBw, rateWord, deviation and preScale. // Refer to RD1155 Rev 1.1 Section 3.2.4.2 .commandNo = 0x3807, .status = 0x0000, .pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx .startTime = 0x00000000, .startTrigger.triggerType = 0x0, .startTrigger.bEnaCmd = 0x0, .startTrigger.triggerNo = 0x0, .startTrigger.pastTrig = 0x0, .condition.rule = 0x1, .condition.nSkip = 0x0, .modulation.modType = 0x1, .modulation.deviation = 600, .symbolRate.preScale = 8, .symbolRate.rateWord = 262144, .rxBw = 0x30, .preamConf.nPreamBytes = 0x6, .preamConf.preamMode = 0x1, .formatConf.nSwBits = 0x20, .formatConf.bBitReversal = 0x0, .formatConf.bMsbFirst = 0x1, .formatConf.fecMode = 9, .formatConf.whitenMode = 0x0, .config.frontEndMode = 0x0, .config.biasMode = 0x1, .config.frontEndMode = 0x02, // Single-ended Mode RFN. .config.bNoFsPowerUp = 0x0, .txPower = 0x23F, .pRegOverride = (uint32_t*)PHY_900M_4_fsk_pOverrides, .centerFreq = 915, .intFreq = 0x0A66, .loDivider = 0x05, }; static const uint32_t PHY_900M_4_fsk_pOverrides[] = { // PHY: Use MCE RAM patch, RFE RAM patch MCE_RFE_OVERRIDE(1, 0, 0, 1, 0, 0), // Rx: Set anti-aliasing filter bandwidth to Maximum ADI_HALFREG_OVERRIDE(0,61,0xF,0x0), // Synth: Set recommended RTRIM to 7 HW_REG_OVERRIDE(0x4038,0x0037), // Synth: Configure fine calibration setting HW_REG_OVERRIDE(0x4020,0x7F00), // Synth: Configure fine calibration setting HW_REG_OVERRIDE(0x4064,0x0040), // Synth: Set Fref to 4 MHz (uint32_t)0x000684A3, // Synth: Configure fine calibration setting (uint32_t)0xC0040141, (uint32_t)0x0533B107, // Synth: Set loop bandwidth after lock (uint32_t)0xA480583, (uint32_t)0x7AB80603, // Synth: Configure VCO LDO (in ADI1, set VCOLDOCFG=0x9F to use voltage input reference) ADI_REG_OVERRIDE(1,4,0x9F), // Synth: Configure synth LDO (in ADI1, set SLDOCTL0.COMP_CAP=1) ADI_HALFREG_OVERRIDE(1,7,0x4,0x4), // Rx: Set LNA bias current trim offset to 3 (uint32_t)0x00038883, // Rx: Set RSSI offset to adjust reported RSSI (uint32_t)0x00FB88A3, // Synth: Use 24 MHz XOSC as synth clock, enable extra PLL filtering (uint32_t)0x02010403, // Synth: Configure extra PLL filtering (uint32_t)0x00108463, // Synth: Increase synth programming timeout (0x04B0 RAT ticks = 300 us) (uint32_t)0x04B00243, /* #### scc: See software-dl.ti.com/.../packet-format.html * for a discussion of Sync Words. */ //Configure threshold for Sync word detection HW_REG_OVERRIDE(0x5104, 0x302B), // Original - restored due to Address filtering implementation, thereby reducing/eliminating false syncs // HW_REG_OVERRIDE(0x5104, 0x7F7F), // MAX - results in zero detections // HW_REG_OVERRIDE(0x5104, 0x6056), // 2 x original - results in zero detections // HW_REG_OVERRIDE(0x5104, 0x4840), // 1.5 x original - results in intermittent detections (approx. 20%) // HW_REG_OVERRIDE(0x5104, 0x4038), // 1.5 x original - results in intermittent detections (approx. 20%) //Set FIFO threshold (uint32_t) 0x002C82C3, (uint32_t) 0x002882D3, // Rx: Do NOT Freeze RSSI on sync found event HW_REG_OVERRIDE(0x6084,0x25F1), // ****PA Ramping overrides HW_REG_OVERRIDE(0x6088,0x4121), HW_REG_OVERRIDE(0x608C,0x0A12), // ****Length of CW tone HW_REG_OVERRIDE(0x52B0,0x00F0), // DC estimation HW_REG_OVERRIDE(0x51F8,0x0F90), //Zero IF in TX (uint32_t) 0x00000343, // Tx: Set PA trim to max (in ADI0, set PACTL0=0xF8) ADI_REG_OVERRIDE(0,12,0xF8), // Single-ended Operation ADI_HALFREG_OVERRIDE(0, 16, 0x7, 1), // Output on RFP /* RF Core monitors */ (uint32_t)0x008F88B3, // For RAT_GPO1 // MOD (MCE_GPO0) to RFC_GPO0 DEMOD (MCE_GPO1) to RFC_GPO1 TX (RAT_GPO0) to RFC_GPO2 RX (RAT_GPO1) to RFC_GPO3 // HW_REG_OVERRIDE(0x1110, RFC_DBELL_SYSGPOCTL_GPOCTL0_MCEGPO0 | RFC_DBELL_SYSGPOCTL_GPOCTL1_MCEGPO1 | RFC_DBELL_SYSGPOCTL_GPOCTL2_RATGPO0 | RFC_DBELL_SYSGPOCTL_GPOCTL3_RATGPO1), // Mod and Demod signals from the core do not work for 4-FSK PHY, so no point wasting them when we could be using them for debug test points. // TX (RAT_GPO0) to RFC_GPO2 RX (RAT_GPO1) to RFC_GPO3 HW_REG_OVERRIDE(0x1110, RFC_DBELL_SYSGPOCTL_GPOCTL2_RATGPO0 | RFC_DBELL_SYSGPOCTL_GPOCTL3_RATGPO1), // ##### Inserting here results in PHY failing to load properly/at all // CRC-32. See e2e.ti.com/.../cc1310-crc-for-rfc_cmd_hs_rx_t-rf_cmdrxhs-rfc_cmd_hs_tx_t-rf_cmdtxhs (uint32_t) 0x00208113, // numCrcBits = 32 HW32_ARRAY_OVERRIDE(0x2004,1), (uint32_t) 0x04C11DB7, //CRC32 polynomial (uint32_t) 0xC0040051, (uint32_t) 0xFFFFFFFF, // End Override (uint32_t)0xFFFFFFFF, }; { // 1.5Mbps .phyMode = VOLSHARE_REGMAP_PHY_900M_750KSYM_4FSK, .setup = &Cc1310_Rf900vol_PHY_900M_750KSYM_4fsk_g, .rfMode = &RfSettings_RF_prop_hs_4fsk }, // TI-RTOS RF Mode Object (includes patches for high speed operation) // e2e.ti.com/.../2363574 static const RF_Mode RfSettings_RF_prop_hs_4fsk = { .rfMode = RF_MODE_PROPRIETARY_SUB_1, .cpePatchFxn = &rf_patch_cpe_ghs, .mcePatchFxn = &rf_patch_mce_ghs, .rfePatchFxn = &rf_patch_rfe_ghs, };

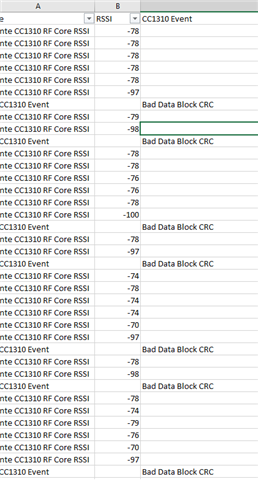

我们从发射对讲机发送的两个传输是快速连续的(间隔约2毫秒-参见下图)-一个是16字节、另一个是1400字节。 当我将射频内核配置为在发生发现同步字事件时不冻结 RSSI 时、接收 CC1310报告的 RSSI 对于16字节数据包接收(约-77dBm)、有时对于较长的传输(即强25%、弱75%)始终为"强"。 请参见所附的说明- CC1310射频内核报告的 RSSI 似乎正确、因为它伴随 bCrcErr = 1而来(例如~μ V-95dBm、比几毫秒前收到的传输低大约20dB)。

当我配置

// Rx: Freeze RSSI on sync found event HW_REG_OVERRIDE(0x6084,0x35F1),

我看到所有短距离和长距离传输的"弱"(<=-89dBm) RSSI 报告。 RFC_hsRxStatus_t* rxStatusHsPtr->STATUS.bCrcErr 的设置适用于大多数较长的传输(不适用于较短的传输)(我正在使用 rf_cmdRxHs.rxConf.bIncludeCrc = 1;)、并且数据包丢失。 我尝试了前导码长度(例如128个符号、256个符号)、但没有改进。

这种 症状是否表明 接收对讲机中的 AGC/ALC 环路滤波器带宽过宽?

我是否有正确的 FEC 模式("9")和白化("0")设置? 这些记录是否充分、使我可以试验和理解他们的行为、或者您是否建议反对这些记录? 另外、由于我打算发送最小长度为1400字节(也许最多8000字节)的数据包、对于传输的长度是否有建议的限制或者它最终是否受用于存储出站数据的可用存储器大小的限制? 是否可以采用各种 FEC 方案来避免瞬时噪声突发导致整个(例如8000字节)数据包丢失的情况? 或者4-FSK PHY 模式是否实现数据白化技术?

很抱歉所有问题-如果您有任何指导、我们将不胜感激。

请告知。

TIA、

Sean。