工具与软件:

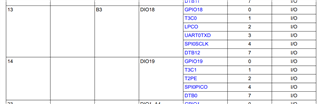

根据数据表、我将在空项目中使用此代码在 DIO8到 DTB3引脚上产生1Hz 输出:

//...

/*

*在 Board_init ()之后添加以下内容;

*确保下方使用的 IOID 未被 PIN 或中的任何条目使用

*板级配置文件中的 GPIO 表。

*时钟源可以使用恒定 clockSrc 进行切换。

*/

// uint8_t clockSrc = 0xC;//对于 HF 晶体时钟除以8

uint8_t clockSrc = 0xF;//对于 LF 晶振时钟

//首先将输出驱动为低电平

GPIO_setConfig (8、GPIO_CFG_OUTPUT | GPIO_CFG_OUT_LOW);

//配置 IOC.IOC3.PORTCFG MMR 以选择 DTB

HWREG (IOC_BASE + IOC_O_IOC3)&&~IOC_IOC3_PORTCFG_M;

HWREG (IOC_BASE + IOC_O_IOC3)|= IOC_IOC3_PORTCFG_DTB;

//确保在 IOC 中选择 DTB 多路复用器(如果需要

//源时钟 IP)在 DTB0上被驱动时复位。

// ULLSEL 多路复用选择(选择 CKMD)

HWREG (IOC_BASE + IOC_O_DTBCFG)&=~IOC_DTBCFG_ULLSEL_M;

HWREG (IOC_BASE + IOC_O_DTBCFG)|= 0x1 << IOC_DTBCFG_ULLSEL_S;// 0x1将 CKMD 路由到 DTB3

//启用 IOC.DTBOE.EN0

HWREG (IOC_BASE + IOC_O_DTBOE)&&~IOC_DTBOE_EN3_M;

HWREG (IOC_BASE + IOC_O_DTBOE)|= IOC_DTBOE_EN3_EN;

//选择要在 DTB3上输出的时钟(CKMD)(DTB[0])

HWREG (CKMD_BASE + CKMD_O_DTBCTL)且=~CKMD_DTBCTL_CLKSEL_M;

HWREG (CKMD_BASE + CKMD_O_DTBCTL)|=(clockSrc)<< CKMD_DTBCTL_CLKSEL_S;

//启用 DTB 输出

HWREG (CKMD_BASE + CKMD_O_DTBCTL)并且=~CKMD_DTBCTL_EN_M;

HWREG (CKMD_BASE + CKMD_O_DTBCTL)|= CKMD_DTBCTL_EN;

//...

这段代码中有什么问题? 我无法生成1Hz 输出。