Other Parts Discussed in Thread: TXS0108E

工具/软件:

您好、

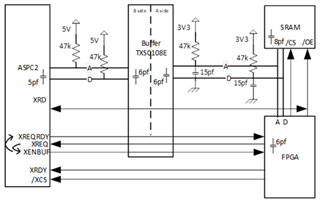

在我的设计中、我当前使用的是缓冲器双向 TXS0108E、没有方向控制信号。

在 VCCB 侧、ASIC 以5V 电压供电、在 VCCAR 侧、FPGA + SRAM 由3V3供电。

每侧都有47k Ω 的上拉电阻器。

我想知道从 A 侧到 B 侧再向 A 侧发送数据之间需要等待多少时间、我只能在数据表中填充传播时间。

感谢您的反馈、

此致

Denis

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TXS0108E

工具/软件:

您好、

在我的设计中、我当前使用的是缓冲器双向 TXS0108E、没有方向控制信号。

在 VCCB 侧、ASIC 以5V 电压供电、在 VCCAR 侧、FPGA + SRAM 由3V3供电。

每侧都有47k Ω 的上拉电阻器。

我想知道从 A 侧到 B 侧再向 A 侧发送数据之间需要等待多少时间、我只能在数据表中填充传播时间。

感谢您的反馈、

此致

Denis

您好、Jack、

B 侧有一个 ASIC 元件(ASPC2 5V)、每个地址/数据信号上都有47k 外部上拉电阻器。

一侧有一个以3V3供电的 FPGA 和 SRAM。

在正常工作模式下、ASPC2通过缓冲器 TXS0108E 从 SRAM 读取/写入数据、有时、FPGA (A 侧)在 SRAM (也是一侧)中写入和读取数据。

ASPC2芯片选择由 FPGA 通过3V3信号直接驱动(与来自 ASPC2的 CS/ IN TTL 5V 兼容)、以确保在 FPGA 读取/写入 SRAM 时 ASPC2地址/数据以 Hz 为单位。

我在应用中看到、并非在 A 侧和 B 侧都可以使用47k Ω 的外部上拉电阻器。

感谢您的反馈

在我们的设计中、它是连接外部上拉电阻器的理想选择、并且根据文档 scea054a.pdf 中的定义、允许使用该值(47k)。

我们的总线工作频率为15.625Mb/s

"切换方向的时间不短"->切换方向的时间是否最长? 我的意思是,如果 B 侧有一个未被选择的组件(以 Hz 为单位),所以由于上拉,SOEM 信号可以从低到高,这种情况下 TX 组件可以检测到从低到高的转换,这种组件可以在30ns 内强制 A 侧为高电平? 即使 B 端 SRAM 存储器施加了低电平?

谢谢

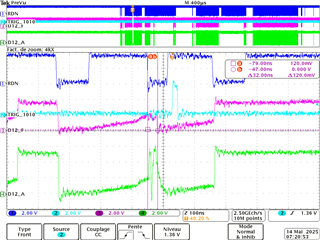

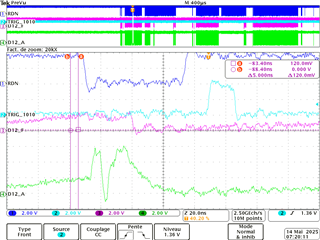

蓝色暗 RDN:用于管理 SRAM 和 ASPC2的信号

Pink D12_F:data12 FPGA 端

绿色 D12_A:数据12 ASPC2侧

蓝光 TRIG_1010:由 FPGA 管理到 TRIG 故障的信号

我的理解是 、如果最后一个数据值状态为低电平、并且由于上拉和寄生电容、所有总线都以 Hz (两侧)为单位进行设置、则缓冲器(无论哪一侧)会检测到信号从低电平缓慢上升到高电平到高电平的转换。

在一侧(例如 ASPC2侧)检测到转换、因此在我猜测接近30ns 时会在另一侧(SRAM 侧)状态为高电平、但在这段时间内、如果 SRAM 也施加低电平、则会出现总线争用。