Other Parts Discussed in Thread: TMUX7201

工具/软件:

我认为 TMUX7201 模型不完整。 从 TI 下载 TMUX7201 PSPICE 模型时、我 在尝试运行仿真时遇到了这个错误:

"实例`X_U14'引用了未定义的模型或子电路"elay_sw_S1D1"`D。 在`D仿真之前、请`D包含"elay_SW_S1D1"定义的文件、或定义"elay_SW_S1D1"。"

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Linh:

我认为这可能是问题所在。

我不熟悉获取 pspice 文件并在节奏中使用它、但我正在研究它、并发现它可能很难实际执行。

首先、您是否有可能在 SPICE 中使用 TMUX7201 SPICE、因为这是我们严格评估这些模型的内容?

请告诉我、我可以提供帮助

此致、

Kameron

尊敬的 Kameron:

很遗憾、我需要 Cadence 进行仿真... 我尝试了两种方法:(1)移除 NC 输出(模型中目前有2个)、(2)移除发生错误的行(X_U14 SW_S1D1_L VDD GND SW_S1D1 DELAY_SW_S1D1)、仿真运行良好(尽管输出错误)。

我不确定这是否有助于排除故障。 尽管如此、Cadence 给出的错误似乎表明 pspice 代码中提到了"Delay_SW_S1D"、但并未在任何地方定义。 这就是为什么当我删除包含"Delay_SW_S1D"的行时、它没有错误地运行...

请告诉我,如果这给你一些想法/如果有什么我可以尝试在我的结束

此致、

LINH

尊敬的 Linh:

深入研究了这个问题之后、您最初的想法是正确的、认为模型缺少了 DELAY_SW_S1D1 subckt 块。

在 pspice 中运行此设备时、缺少的文本不会影响仿真、但根据我的团队的理解、这可能会影响您在中使用模型的其他环境

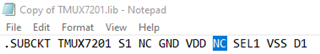

这是我添加到该文件中的文本、该文本应该可以修复错误

*buffer

VDD GND 输出中的.SUBCKT DELAY_SW_S1D1

*

C1 OUT_ONDLY GND 1e-09

Eron NRON GND 表{V (VDD、GND)}=

+(12、10.0)

+(15、10.0)

+(20、10.0)

+(44,10.0)

10E9中的 R1 OUT_ONDLY

GRON OUT_ONDLY in 值={V (OUT_ONDLY、in)/V (NRON)}

*

EOUT_ONREC OUT_ONREC GND 值={V (OUT_ONDLY、GND)}

*

GND SWON 中的 S_ON OUT_ONREC OUT

.model SWON vSwitch roff=1e9、Ron = 0.001、voff = 0.37V、Von = 0.63V

*

C2 OUT_OFFDLY GND 1e-09

EROFF nroff GND 表{V (VDD、GND)}=

+(12、21.519)

+(15、21.519)

+(20、21.519)

+(44、21.519)

10E9中的 R2 OUT_OFFDLY

Groff OUT_OFFDLY in 值={V (OUT_OFFDLY、in)/V (nroff)}

*

EOUT_OFFREC OUT_OFFREC GND 值={V (OUT_OFFDLY、GND)}

*

S_OFF OUT_OFFREC OUT 处于 GND SWOFF

.model SWOFF vSwitch roff=1e9 Ron = 0.001 voff = 0.63V Von = 0.37V

*

结束

这里是我添加此内容的文件。

e2e.ti.com/.../Copy-of-TMUX7201.lib

尝试该文件、查看它是否按节奏工作

如果不是、我可以再次查看并进行更多编辑

请告诉我这是否有帮助!

此致、

Kameron

尊敬的 Linh:

好在这里我们正在接近在这里工作的模型!

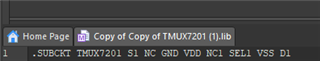

因此、我认为我们唯一需要做的就是更改 其中一个 NC 引脚名称(我将 NC 更改为 NC1 、这应该可以解决节奏中的问题)

NC 引脚未与 TMUX7201内的实际模型块电气连接

这个问题似乎在节奏上很常见、但我认为这应该是一个简单的解决方案。

e2e.ti.com/.../Copy-of-Copy-of-TMUX7201-_2800_1_2900_.lib

请告诉我这是否有效、如果没有、我们可以再看一下