主题中讨论的其他器件: SN74LVC1G66

大家好、

我们是否有任何包含 SN74AUC2G66的 EVM 或参考设计? 我的客户正在寻找示例原理图或应用手册、以便在 绘制原理图时参考。 我在产品文件夹中找不到任何相关文档。 仅供参考、他们使用 SN74AVUC2G66实现 25MHz AVBus 的零延迟缓冲器。 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们是否有任何包含 SN74AUC2G66的 EVM 或参考设计? 我的客户正在寻找示例原理图或应用手册、以便在 绘制原理图时参考。 我在产品文件夹中找不到任何相关文档。 仅供参考、他们使用 SN74AVUC2G66实现 25MHz AVBus 的零延迟缓冲器。 谢谢。

您好 Ella、

您可以在这里进一步介绍一下使用方法吗? 他们是尝试将 SN74AUC2G66用作零延迟缓冲器、还是使用 IS 作为实现零延迟缓冲器的一部分? 只是希望清楚、这是一个无源器件、不会缓冲任何信号。

SN74LVC1G66数据表的应用部分将在此处工作。 唯一的建议是严格遵守数据表限制和电源上的去耦电容。 0.1uF 电容应尽可能靠近器件。

谢谢、

Rami

您好 Rami、

[引用 userid="409034" URL"~/support/switches-multiplexers-group/switches-multiplexers/f/switches-multiplexers-forum/1172605/sn74auc2g66-reference-example-schematic/4413576 #4413576"]只需明确这是一个无源器件,不会缓冲任何信号。我是否可以要求对这一意见作更详细的阐述? "无源器件"和"缓冲任何信号"的确切含义是什么? 它可能与输入阻抗或输出驱动能力有关吗?

它们将使用 SN74AUC2G66 作为零延迟缓冲器。 它们需要在主 SoC 和从器件之间使用它、以实现 AVSBus 系列接口。 我在从 INT-LOGIC 产品线寻找一个最小延迟缓冲 器、但我注意到 SN74AUC2G66具有比其他 INT-LOGIC 器件更短的 TPD 延迟、并选择 SN74AUC2G66作为建议。

Ella、

无源器件只是意味着它是一个模拟开关、基本上可以建模为具有一些电容的电阻器。 此常见问题解答展示了该 [常见问题解答]的一个很好的示例、如何估算模拟开关/多路复用器中的传播延迟和通道间偏差?

因此、您对输出驱动能力是正确的。 模拟(无源)多路复用器将不具有任何输出驱动、而数字多路复用器(您在逻辑产品系列中找到的)将具有任何输出驱动。

两个器件都具有非常低的传播延迟、但两者都很大程度上取决于负载、因为两者都是非常简单的 CMOS 架构。 正如您所看到的、无源器件的电压往往要低一点。

我对零延迟缓冲器的理解是、它们需要具有缓冲时钟输入、该输入被馈送到多个源、但需要一个 PLL 来稳定时钟。 只使用他们现在希望使用的 SPST 多路复用器只能连接/断开时钟、这是不一样的。 这就是为什么我询问它是用作零延迟缓冲器还是用作电路的一部分来支持零延迟缓冲器实现。 您是否有他们想要做什么的方框图?

谢谢、

Rami

您好 Rami、

非常感谢您的评论! 在我与客户讨论时、请让我仔细检查一下。

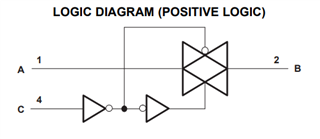

(1)我认为方框图可能会误导他们将 SN74AUC2G66视为双向缓冲器。 该图看起来像一个具有输出驱动能力的缓冲器。 我想知道这 是否是该无源 SPST 的通用图。

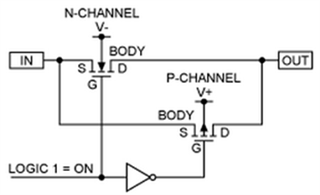

(2)下面是 SPST 开关的简化图。 您能否帮助确认此结构是否也适用于 SN74AUC2G66?

(3)这些问题与 SN74AUC2G66的工作原理有关。

(3)-(1)

当 C = 1 ->通道打开时、

当 A 为驱动器时:B 为高电平--> A 下降至低电平--> A 侧的驱动器从 B 侧吸收电流(通过 n 沟道 FET)--> B 下降至低电平

当 A 为驱动器时:B 为低电平--> A 上升至高电平--> A 侧的驱动器向 B 侧提供电流(通过 p-ch FET)--> B 上升至 高电平

当 B 是驱动器时: A 为高电平--> B 下降至低电平--> B 侧的驱动器从 A 侧吸收电流(通过 p-ch FET)--> A 下降至低电平

当 B 为驱动器时:A 为低 电平--> B 上升 至 高电平 --> B 侧的驱动 器向 A 侧提供电流(通过 n 沟道 FET)--> A 上升 至高电平

(3)-(2)

它们是否可以混合 A/B 引脚的上拉和下拉? 我们可以假设 A 侧通过4.7k Ω 上拉至1.8V、而 B 侧通过4.7k Ω 下拉至 GND。 当 A 侧和 B 侧的驱动器都处于高阻态时、A/B 引脚将通过电阻器除以(RDSon 被忽略)显示0.9V (1.8V/2)。 我的理解是否正确?

此致、

Ella

您好 Ella、

1-2:

我肯定会看到这会令人困惑。 您可以看到、第二个图像(传输门架构)是一个很好的可使用的简化图。

3.1-3.2:

您的假设就在这里。 A 侧和 B 侧短路。 但实际看到的情况在技术上取决于驱动器的阻抗和任何上拉/下拉电阻器。 话虽如此、在您的示例中、您是正确的。 您可以在一侧放置一个上拉电阻器、在另一侧放置一个下拉电阻器、并创建一个分压器。 当然、正如您提到的、RDS (on)会被忽略、因此您不会达到0.9V。

谢谢、

Rami