主题中讨论的其他器件: TS5MP646

大家好、团队、

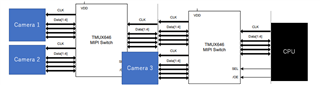

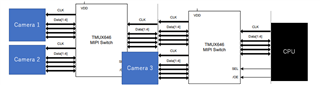

我的客户正在考虑使用2 个 TMUX646在3个用于 CPU 的摄像头之间切换、如下图所示。

他将把它们用于 MIPI D-PHY HS。

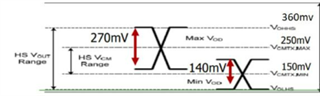

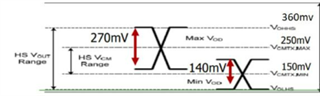

客户担心电压电平在经过2个 TMUX646之后是否会降低、并且 可能无法满足 MIPI D-PHY HS 的 Vpp 或压摆率重新配置(最小值140mVpp)。

它是否会满足此配置中的 MIPI 规格?

此致、

基宽原

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

我的客户正在考虑使用2 个 TMUX646在3个用于 CPU 的摄像头之间切换、如下图所示。

他将把它们用于 MIPI D-PHY HS。

客户担心电压电平在经过2个 TMUX646之后是否会降低、并且 可能无法满足 MIPI D-PHY HS 的 Vpp 或压摆率重新配置(最小值140mVpp)。

它是否会满足此配置中的 MIPI 规格?

此致、

基宽原

嘿、Kei、

它们使用的频率是多少? 我正在寻找每通道频率、而不是总带宽(请参阅 [常见问题解答]如何根据协议的数据速率选择合适的模拟开关/多路复用器带宽?)。

MIPI 通常是 DDR 和4个数据通道、因此无论带宽是多少、您都应该在每个时钟周期内除以4个通道和2个读数(共8个)。

鉴于 MIPI 通常以4.5GHz 的频率进行最大频率输出、我怀疑它们所使用的最大频率为每通道~560MHz。

了解这一点后、在级联多路复用器时、您肯定会产生额外的损耗。 当然、损耗的大小取决于该频率。 我发现类似器件的类似帖子、即之前版本的 TMUX646、TS5MP646

从上面完成的测试来看、它们可以预期插入损耗的两倍、从500MHz 时的~-0.75dB 到~-1.5dB。 如果输入为270mV、我的数学结果是大约45mV 的压降。 当然、这不会考虑延伸布线产生的额外损耗。 我建议将这些器件尽可能靠近、以确保布线长度尽可能短。 但是、对于 MIPI 可接受的阈值、我不太熟悉。 该压降是否太大? 或者、您知道我们正在处理的范围是什么吗?

谢谢、

Rami