您好、专家、

我们需要您为客户的应用提供帮助。

他们 目前正在开发某种测量电子产品。 其基本理念如下:他们希望采用高精度 ADC。 它们希望将该 ADC 的一个输入乘以某种电路。 因此、一个 ADC 也成为 n 个数。 在这里、模拟多路复用器已使我的眼睛受到了积极的影响。 例如 TMUX6208。 以下规格位于我的要求列表中:

此致、

Jonathan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、专家、

我们需要您为客户的应用提供帮助。

他们 目前正在开发某种测量电子产品。 其基本理念如下:他们希望采用高精度 ADC。 它们希望将该 ADC 的一个输入乘以某种电路。 因此、一个 ADC 也成为 n 个数。 在这里、模拟多路复用器已使我的眼睛受到了积极的影响。 例如 TMUX6208。 以下规格位于我的要求列表中:

此致、

Jonathan

这些是产品页面上列出的值。

此培训视频使用更复杂的公式: 2.4带宽、串扰、关断隔离和 THD+Noise

您好、Jonathan、

要说明的是、您是否有任何机会意味着您想要 并联大多数多路复用器? 实际上、8个多路复用器并联连接到1个多路复用器。 或者它们都是串联的? 在串联情况下、每次在信号路径中放置信号开关时、都会引入一些信号损耗和失真。 我们的信号开关数据表对损耗和失真进行了特性描述。 Ron 和 Con 是重要参数。 Ron 损耗 将导致信号振幅降低、而 Con 损耗将导致 信号上升时间更慢。

级联多个器件会在 每个器件上引入损耗。 要确定损耗是否会影响您的电路、您需要查看在 应用中、每个开关上的4 Ω Ron 产生的压降是否显著、以及您是否具有足够的带宽裕度。 当您开始级联多路复用器时、降级会很快增加。 多路复用器的每个实例都是另一个会影响带宽的 RC。 您是否可以为用例提供原理图? 到 您到达第9个多路复用器时、9个串联多路复用器可能会导致大幅降级和带宽衰减。 只需两个串联的级联、每个级联多路复用器的插入损耗就会翻倍。

就带宽而言、数据表中也对其进行了特性描述(第20页)。 由于各种寄生效应、外部电阻和外部电容、实际带宽(33MHz)与"理想"带宽不同。

谢谢!

Alex

尊敬的 Alex:

我们的客户能够检查您的答案、并感谢您的支持。

下面是客户的反馈。

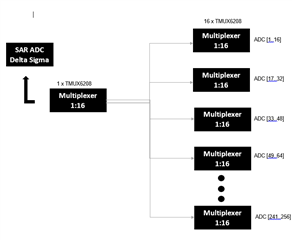

我在这里拍了一张小照片来解释我的用例。 左侧是 ADC (首先、SAR 或 Δ-Σ ADC 无关紧要)。 它具有一个输入、该输入会进入 TMUX6208的第一级。 第一级允许将一个输入复用到16个输入。 TMUX6208多路复用器连接到这些输入。

除此之外、 为了更好地了解多路复用器的串联连接、我下载了 TMUX6208的 P-Spice 模型。 在我第一次尝试时、我的输入与输出相对应。 输入衰减或插入损耗为零。 P-Spice 模型中是否考虑了输入衰减?

非常感谢您迄今提供的非常慷慨的帮助。

此致、

Jonathan

您好、Jonathan、

TMUX6208是一款低导通电阻器件、如果 您在直流电附近工作 、则损耗非常小 并不奇怪 、但损耗并不完全为零。 我可以看到您用于仿真的电路吗? 然后、我将在我们的端部进行仿真、以查看我们得到的结果。

我还注意到您在提供的原理图上说了16个输入和 ADC [241..256]。 与原始帖子中提到的9相比、您实际上需要17 16:1还是33 8:1?

谢谢!

Alex

尊敬的 Alex:

以下是客户提供的更新和示例。

你好、Jonathan、

[引用 userid="470463" URL"~/support/switches-multiplexers-group/switches-multiplexers/f/switches-multiplexers-forum/1190045/tmux6208-multiplication-of-analogue-signals/4490157 #4490157"]但不假设我的信号拾取(ADC/OPV)为高阻抗回顾了我们到目前为止讨论的内容后、我是否可以问我们为什么 不假设 ADC 输入 为高阻抗? 通常情况下、ADC 输入为高阻抗、因此很奇怪。 如果我们考虑到存在高阻抗输入、则此处无需阻抗转换器。

谢谢!

Alex