主题中讨论的其他器件: SN74CBTLV3126

大家好、

我们是否具有路线图器件支持3通道输出并与 TS3DS10224相似?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们是否具有路线图器件支持3通道输出并与 TS3DS10224相似?

尊敬的 Rami:

添加问题:

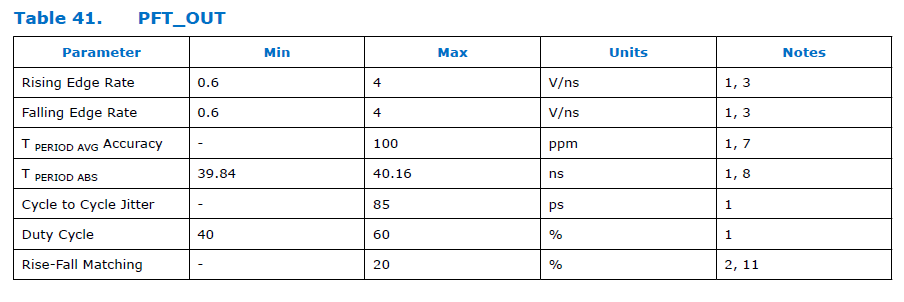

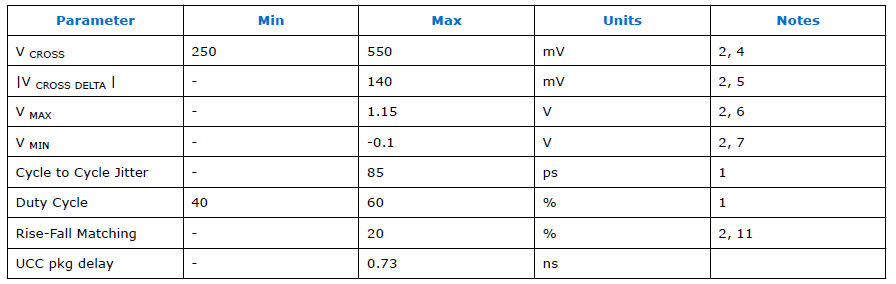

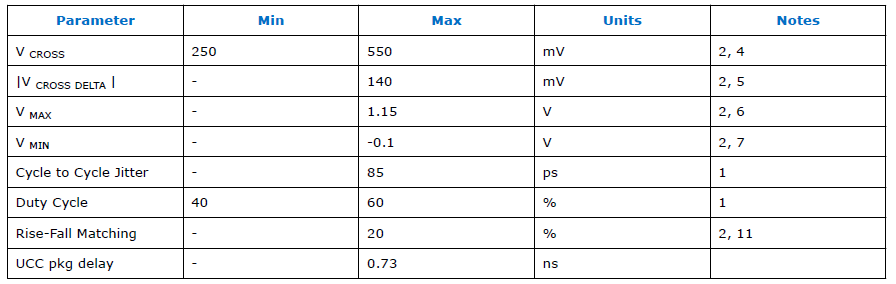

是否可以评估通过 TSDS10224的两个级联后、PFTOUT-DP/N 输出的信号是否可以满足 TSDS10224 XTAL-CLK-P 的要求?

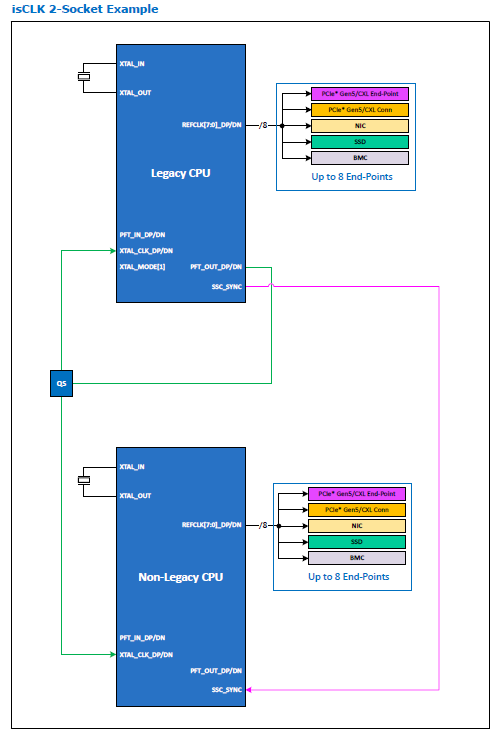

目前,英特尔的演示板使用 PFT。 OUT-DP/N、用于通过第一级 TSDS10224将时钟发送到两个 CPU。 但是、由于需要向其他板发送额外的时钟、该时钟增加到了两个级别。

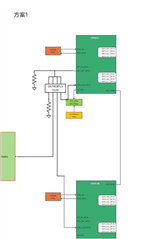

英特尔 PDG 解决方案如下所示:

嘿 Dane、

我可能会误解这里的用例、但想法是将 PFT_OUT 扇出到三个不同的位置?

使用 SN74CBTLV3126的类似解决方案能否正常工作?

在这里、您只需要将输入馈送到全部4个通道。 电容会增加一点、因为从技术上讲、它是相同的总线、但如果周期仅为40ns (25MHz)、则在此实现方案中应该没有问题。

请告诉我您和客户的看法。

如果三个输出之间的延迟和延迟需要达到精确度,那么我们当然希望减少多路复用器级联的使用(请参见此处的应用手册 :使用多路复用器串联设计:级联多路复用器指南)。 不过、我们现在可以选择具有低而平坦的 RON 的多路复用器来帮助降低影响、但我认为上述解决方案可能是实现这一点的最佳方法。

谢谢!

Rami