Other Parts Discussed in Thread: CSD17483F4, TINA-TI

请根据以下要求建议 MOSFET 配置-

24V 继电器详细信息-

1.额定电压(Vdc)- 24V

2.线圈电阻–350欧姆

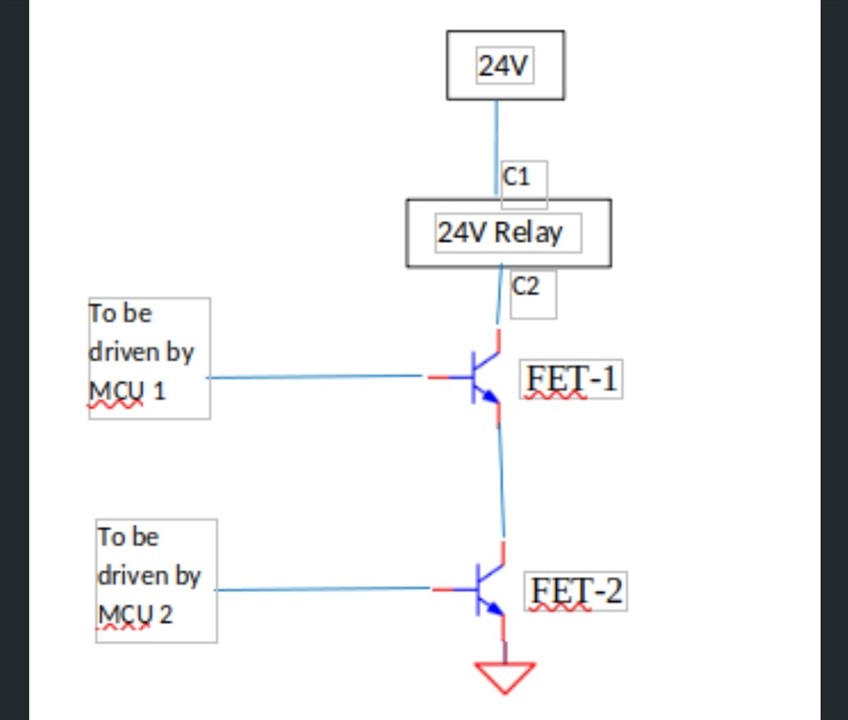

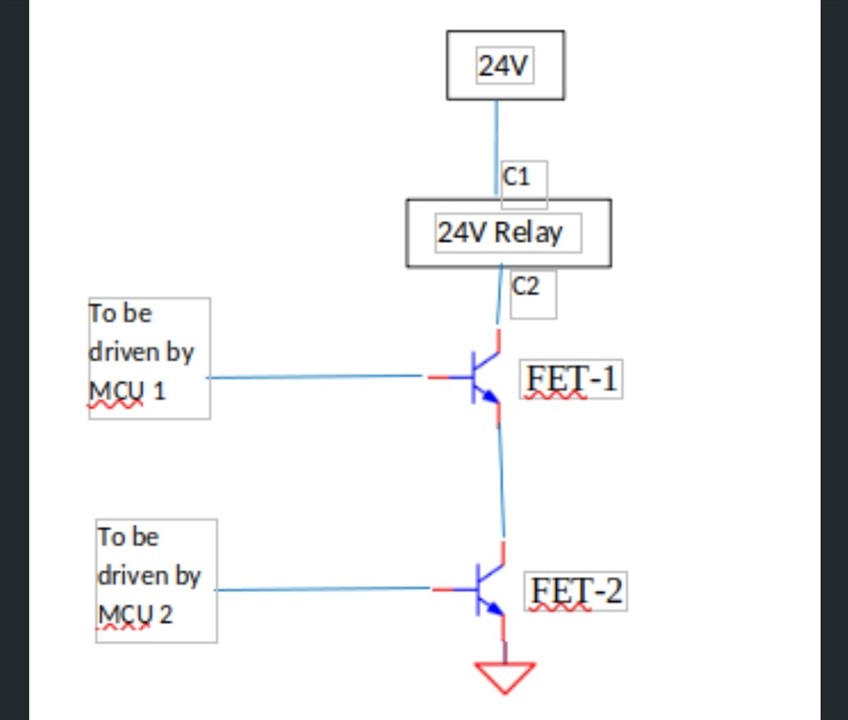

两个 FET 必须由2个不同的 MCU 独立驱动。 当两个 FET 都打开时、24V 继电器应通电。

请建议 FET 和连接配置。

当电源被切断时、两个 FET 都应关闭。

还提供每个 FET 的自检测试程序

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: CSD17483F4, TINA-TI

请根据以下要求建议 MOSFET 配置-

24V 继电器详细信息-

1.额定电压(Vdc)- 24V

2.线圈电阻–350欧姆

两个 FET 必须由2个不同的 MCU 独立驱动。 当两个 FET 都打开时、24V 继电器应通电。

请建议 FET 和连接配置。

当电源被切断时、两个 FET 都应关闭。

还提供每个 FET 的自检测试程序

您好、tirak kc:

感谢您关注 TI FET。 根据您的要求、通过2个串联350Ω 的电流仅约为70mA (24V/FET)。 继电器的24V 输入调节效果如何? MCU 的输出高电压电平是多少? 此应用至少需要一个30V N 沟道 FET。 如果24V 未经过良好调节或瞬变超过30V、则可能需要考虑使用电压更高的 FET。 作为起点、我推荐 CSD17483F4、30V FemtoFET。 这是我们针对此应用的最低成本、最小 FET。 它需要 MCU 提供最低1.8V 的栅极驱动电压。 实现应该非常简单、即将顶部 FET 的漏极连接到继电器线圈、将其源极连接到底部 FET 的漏极。 我建议为每个- 100kΩ 使用一个低值(1 -5Ω)的串联栅极电阻器、并在每个 FET 的栅极到源极之间使用一个更大的(10kΩ FET)下拉电阻器、以确保在栅极保持悬空时将其关闭。 我不确定您会如何执行 FET 自检。 如果您有任何问题、请查看并告诉我。

此致、

约翰·华莱士

TI FET 应用

您好、

要打开 FET1、必须打开 FET2以将 FET1源极拉至 GND。 如果 FET2关闭、则 FET1的源将悬空、无法打开 FET1。 以下是我的建议:

我创建了一个简单的 TINA-TI 仿真、并附上了该仿真附件供您尝试。 我只是使用开关来控制在每个栅极上施加的电压、并假定 VCC = 1.8V。 您可以通过单击开关来更改它们的状态。 我还添加了 SW4和 SW5、以便您短接一个或两个 FET、因为这是功率 MOSFET 的典型故障模式。 运行直流分析以计算节点电压、并使用探头查看电路中任何节点的电压。 开关当前配置为使两个 FET 都导通。

您可以通过以下链接下载并安装 TINA-TI:

https://www.ti.com/tool/TINA-TI?keyMatch=TINA

如果您有任何问题、请告诉我。

谢谢。

约翰

您好、John Wallace1:

很抱歉这么晚才回复。

感谢您的转发。 TSC 设计。

我在 TINA 中测试了上述电路、并测试了不同的故障条件。

我想在不同的 FET 短路情况下监测 VM 引脚的电压。

当底部 FET 短路时- VM 引脚将为0V

当顶部 FET 短路时、VM 引脚的电压为24V

如果两个 FET 都没有短路、VM 引脚将大约为7.2V。

VM 引脚将在 MCU 中使用 ADC 引脚进行监控、您能建议一种方法来限制 MCU 引脚上 VM 引脚的电压吗?

通过使用分压器/齐纳二极管来防止 MCU 引脚上的过压损坏。

谢谢。

蒂拉克