亲爱的TI工程师们你们好:

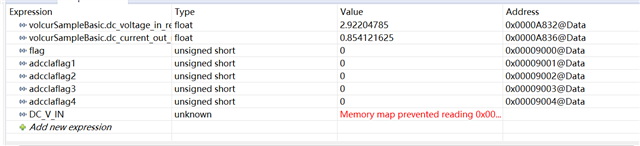

我最近在用TI的28p55 launchpad ,在进行CPU-CLA-DMA测试的时候,为了兼顾CLA和DMA能同时读取ADC结果寄存器的数据,所以将数据放在了 起始地址在0x001700的DMAtoCLA MSG RAM中(cmd文件中为:DMATOCLARAM : origin = 0x001700, length = 0x000080),虽然程序可以正常运行,但是在仿真时就看不到变量了,提示是:Memory map prevented reading 0x00001700@Data,因此想来咨询一下有没有解决方法,谢谢!

我修改后的cmd文件、仿真时遇到的提示信息如下:

CLA_SCRATCHPAD_SIZE = 0x300;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002 // Update the codestart location as needed

BOOT_RSVD : origin = 0x000002, length = 0x000126 /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x000128, length = 0x0002D8

RAMM1 : origin = 0x000400, length = 0x000400

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMLS8 : origin = 0x014000, length = 0x002000 // When configured as CLA program use the address 0x4000

RAMLS9 : origin = 0x016000, length = 0x002000 // When configured as CLA program use the address 0x6000

//RAMLS8_CLA : origin = 0x004000, length = 0x002000 // Use only if configured as CLA program memory

// RAMLS9_CLA : origin = 0x006000, length = 0x002000 // Use only if configured as CLA program memory

RAMGS0 : origin = 0x00C000, length = 0x002000 //可以DMA访问

RAMGS1 : origin = 0x00E000, length = 0x002000 //可以DMA访问

RAMGS2 : origin = 0x010000, length = 0x002000

RAMGS3 : origin = 0x012000, length = 0x002000 //可以DMA访问

/* Flash Banks (128 sectors each) */

FLASH_BANK0 : origin = 0x080002, length = 0x1FFFE

FLASH_BANK1 : origin = 0x0A0000, length = 0x20000

FLASH_BANK2 : origin = 0x0C0000, length = 0x20000

FLASH_BANK3 : origin = 0x0E0000, length = 0x20000

FLASH_BANK4 : origin = 0x100000, length = 0x07FFF

CLATOCPURAM : origin = 0x001480, length = 0x000080 //CPU和CLA都能访问

CPUTOCLARAM : origin = 0x001500, length = 0x000080 //CPU和CLA都能访问

CLATODMARAM : origin = 0x001680, length = 0x000080 //CPU CLA DMA都能访问

DMATOCLARAM : origin = 0x001700, length = 0x000080 //CPU CLA DMA都能访问

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN

.text : >> FLASH_BANK0 | FLASH_BANK1, ALIGN(8)

.cinit : > FLASH_BANK0, ALIGN(8)

.switch : > FLASH_BANK0, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

.bss : > RAMLS5

.bss:output : > RAMLS3

.init_array : > FLASH_BANK0, ALIGN(8)

.const : > FLASH_BANK0, ALIGN(8)

.data : > RAMLS5 | RAMLS6

.sysmem : > RAMLS4

ramgs0 : > RAMGS0

ramgs1 : > RAMGS1

ramgs2 : > RAMGS2

CLADATARAM :> DMATOCLARAM

// .scratchpad : > RAMLS2

.bss_cla : > RAMLS2

GROUP

{

.TI.ramfunc

ramfuncs

dclfuncs

} LOAD = FLASH_BANK0,

RUN = RAMLS0|RAMLS1,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

GROUP

{

isrcodefuncs

} LOAD = FLASH_BANK1,

RUN = RAMLS3,

LOAD_START(isrcodefuncsLoadStart),

LOAD_SIZE(isrcodefuncsLoadSize),

LOAD_END(isrcodefuncsLoadEnd),

RUN_START(isrcodefuncsRunStart),

RUN_SIZE(isrcodefuncsRunSize),

RUN_END(isrcodefuncsRunEnd),

ALIGN(8)

Cla1Prog : LOAD = FLASH_BANK1,

RUN = RAMLS8,

LOAD_START(Cla1ProgLoadStart),

RUN_START(Cla1ProgRunStart),

LOAD_SIZE(Cla1ProgLoadSize),

ALIGN(4)

.const_cla : LOAD = FLASH_BANK1,

RUN = RAMLS2,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

ALIGN(4)

CLAscratch :

{ *.lib(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.lib(CLAscratch_end) } > RAMLS1

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

谢谢TI的工程师,还请赐教!