Part Number: C2000WARE

您好,

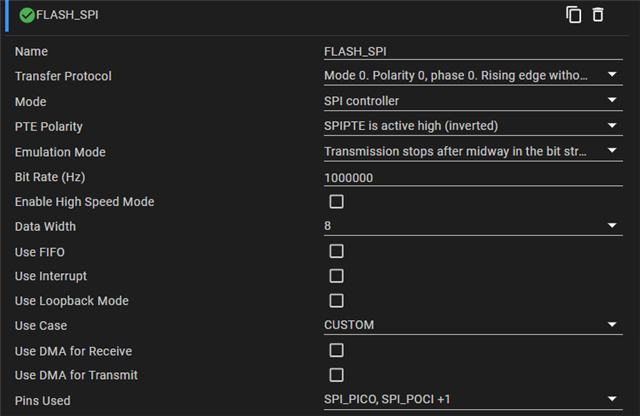

我在使用F28P650DK9,封装为169引脚的芯片的引脚55、56、57、58为一组的SPI,在使用中发现读取数据异常,通过示波器抓取发现存在数据波形仅能够拉高至1.3V左右,工程配置如下图:

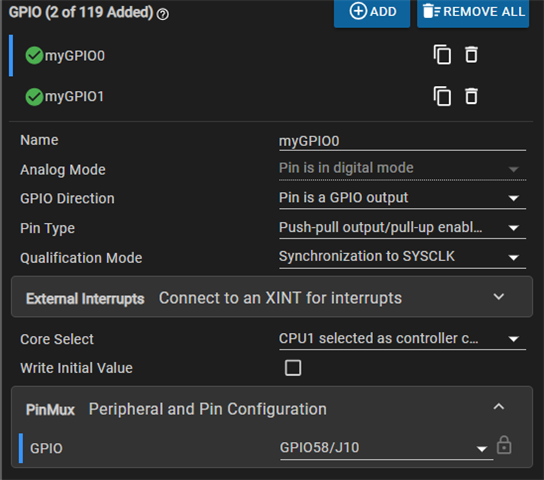

随后我尝试通过使用GPIO推挽输出高电平的方式将55、58引脚拉高;

结果发现,55引脚能够被拉高至3.3v,58引脚则一直处于低电平;

我们还测试63、64、65、66为一组的SPI以及69、70、71、72的一组SPI,都存在某一个引脚电平拉不起来的情况;

麻烦帮忙测试验证一下;