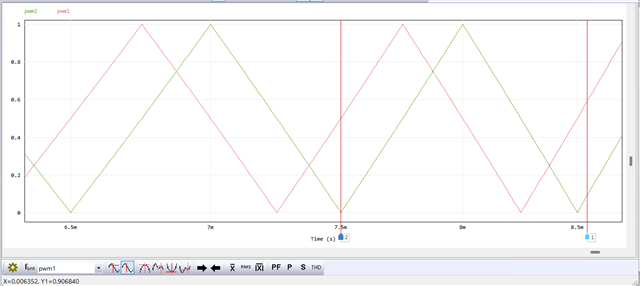

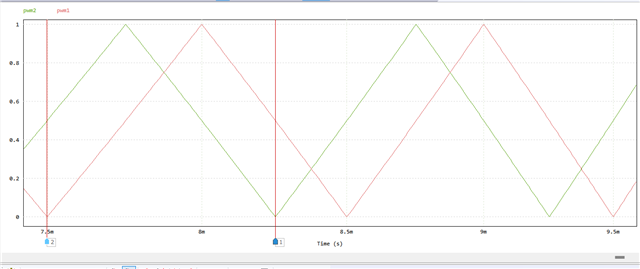

配置描述描述:在项目中使用PWM调频移相,PWM1 与PWM2 ,

①设置PWM2为同步源 ,使用的是 GLDCTL2[OSHTLD]=1 , GLDCTL[GLDMODE]=0,CNT=0输出同步信号;

② PWM2当CNT=0,且GLDCTL2[OSHTLD]=1,全局加载,PWM1 接受到同步信号,并且GLDCTL2[OSHTLD]=1 ,全局加载;

③配置使用adc中断,当PWMCNT==PRD 时产生中断,计算周期和移相角

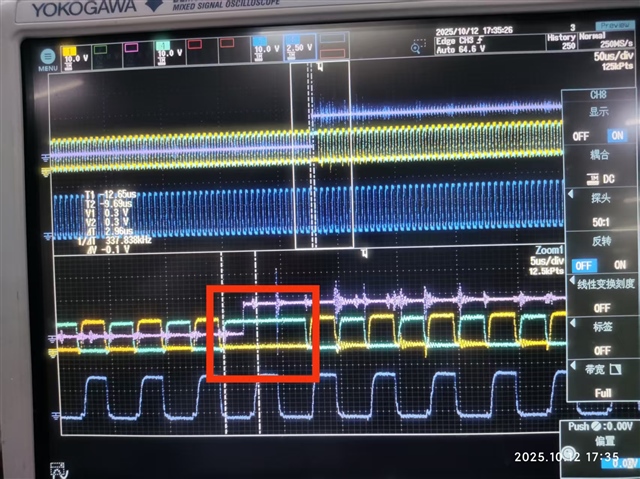

问题描述,当TBPHS从0变为1时,输出电平持续为高,请帮忙分析原因,以及解决方法

pwm配置如下

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYSCLKOUT

EPwm1Regs.TBPRD = SRC_Period_min;

EPwm1Regs.TBPHS.all = 0;

EPwm1Regs.TBCTR = 0x0000;

// Setup TBCLK

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.EPWMSYNCINSEL.bit.SEL=SYNC_IN_SRC_SYNCOUT_EPWM2; //ͬ��ԴEPWM2

EPwm1Regs.EPWMXLINK.bit.GLDCTL2LINK=1; //link EPWM2

EPwm1Regs.EPWMXLINK.bit.TBPRDLINK=1; //link EPWM2

EPwm1Regs.GLDCTL.bit.GLD=1;

EPwm1Regs.GLDCTL.bit.GLDMODE=0x3; //ͬ�����ز���ʱ��

EPwm1Regs.GLDCTL.bit.OSHTMODE=1;

EPwm1Regs.GLDCFG.all=0xF; //globle load

// Set actions

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLA.bit.PRD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLB.bit.PRD = AQ_CLEAR;

EPwm1Regs.AQTSRCSEL.bit.T1SEL = 7;

EPwm1Regs.DBCTL.bit.IN_MODE = 2;

EPwm1Regs.DBCTL.bit.POLSEL = 2;

EPwm1Regs.DBCTL.bit.OUT_MODE = 3;

EPwm1Regs.DBFED.bit.DBFED = SRC_Period_min; //12=0.1us*120M

EPwm1Regs.DBRED.bit.DBRED = SRC_Period_min;

EPwm1Regs.AQSFRC.bit.RLDCSF=CC_CTR_PRD; //�������

EPwm1Regs.AQCSFRC.all = 0x09; //force low

//===========================================================================

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYSCLKOUT

EPwm2Regs.TBPRD = SRC_Period_min;

EPwm2Regs.TBPHS.all = 0;

EPwm2Regs.TBCTR = 0x0000;

// Setup TBCLK

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm2Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Master module

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

// EPwm2Regs.TBCTL2.bit.PRDLDSYNC=0x0; //TBPRD���������

EPwm2Regs.EPWMSYNCOUTEN.bit.ZEROEN=1; //ͬ���źŹ�������

EPwm2Regs.TBCTL2.bit.OSHTSYNCMODE=1;

EPwm2Regs.TBCTL3.bit.OSSFRCEN=1;

EPwm2Regs.GLDCTL.bit.GLD=1;

EPwm2Regs.GLDCTL.bit.GLDMODE=0x0; //ͬ������CTR=0;

EPwm2Regs.GLDCTL.bit.OSHTMODE=1;

EPwm2Regs.GLDCFG.all=0xF; //globle load

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Set actions

EPwm2Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm2Regs.AQCTLA.bit.PRD = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET;

EPwm2Regs.AQCTLB.bit.PRD = AQ_CLEAR;

EPwm2Regs.DBCTL.bit.IN_MODE = 2;

EPwm2Regs.DBCTL.bit.POLSEL = 2;

EPwm2Regs.DBCTL.bit.OUT_MODE = 3;

EPwm2Regs.DBFED.bit.DBFED = SRC_Period_min; //12=0.1us*120M

EPwm2Regs.DBRED.bit.DBRED = SRC_Period_min;

EPwm2Regs.AQSFRC.bit.RLDCSF=CC_CTR_PRD; //�������

EPwm2Regs.AQCSFRC.all = 0x09; //force low

中断程序

interrupt void adc_isr(void)

{

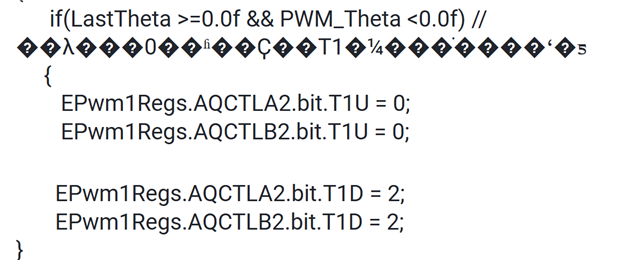

if(LastTheta >=0.0f && PWM_Theta <0.0f) //��λ���0��ʱ��Ҫ��T1�¼���ֹ����ߵ�ƽ

{

EPwm1Regs.AQCTLA2.bit.T1U = 0;

EPwm1Regs.AQCTLB2.bit.T1U = 0;

EPwm1Regs.AQCTLA2.bit.T1D = 2;

EPwm1Regs.AQCTLB2.bit.T1D = 2;

}

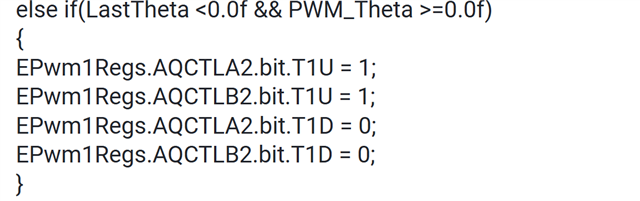

else if(LastTheta <0.0f && PWM_Theta >=0.0f)

{

EPwm1Regs.AQCTLA2.bit.T1U = 1;

EPwm1Regs.AQCTLB2.bit.T1U = 1;

EPwm1Regs.AQCTLA2.bit.T1D = 0;

EPwm1Regs.AQCTLB2.bit.T1D = 0;

}

else

{

EPwm1Regs.AQCTLA2.bit.T1U = 0;

EPwm1Regs.AQCTLB2.bit.T1U = 0;

EPwm1Regs.AQCTLA2.bit.T1D = 0;

EPwm1Regs.AQCTLB2.bit.T1D = 0;

}

if(PWM_Theta <= 0.0f) //�����ͺ�ԭ�ߣ���طŵ�

{

EPwm1Regs.TBCTL.bit.PHSDIR = TB_UP; //����

EPwm1Regs.TBPHS.bit.TBPHS = (-PWM_Theta)*SRC_Period;

}

else //���߳�ǰԭ�� ��س��

{

EPwm1Regs.TBCTL.bit.PHSDIR = TB_DOWN; //�½�

EPwm1Regs.TBPHS.bit.TBPHS = PWM_Theta*SRC_Period;

}

EPwm2Regs.TBPRD = SRC_Period;

EPwm2Regs.GLDCTL2.bit.OSHTLD = 1;

LastTheta=PWM_Theta;

}

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

驱动1A1B异常