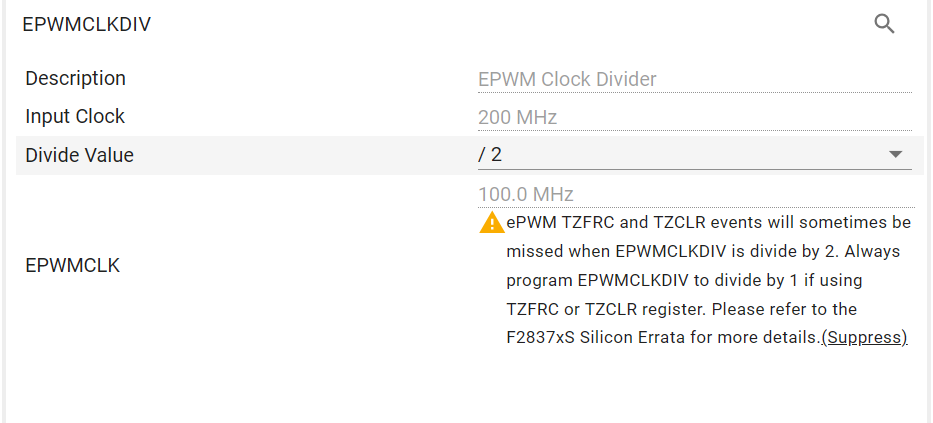

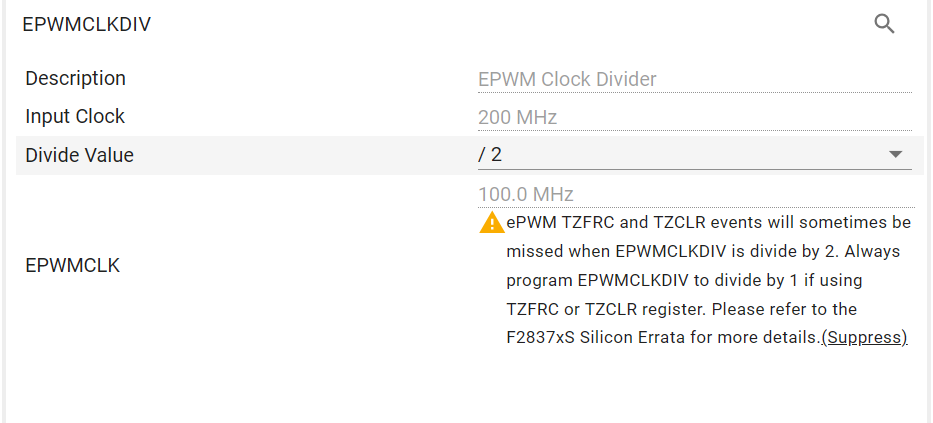

ePWM时钟 EPWMCLKDIV 2分频时 提示 会错过TZFRC和TZCLR , 所以如果要使用TZFRC的话,EPWMCLKDIV只能是1分频吗? 如果设为1分频,但是pwm时钟又不能超过100MHZ,所以CPUCLK都只能设为100MHZ了, 这显然是不可取的, 极大限制了性能, 所以有什么别的办法,在保证CPUCLK为200MHz的情况下,正常使用ePWM的TZFRC和TZCLR . 感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

ePWM时钟 EPWMCLKDIV 2分频时 提示 会错过TZFRC和TZCLR , 所以如果要使用TZFRC的话,EPWMCLKDIV只能是1分频吗? 如果设为1分频,但是pwm时钟又不能超过100MHZ,所以CPUCLK都只能设为100MHZ了, 这显然是不可取的, 极大限制了性能, 所以有什么别的办法,在保证CPUCLK为200MHz的情况下,正常使用ePWM的TZFRC和TZCLR . 感谢!

您好,

这位用户和您的问题类似,请参考这个帖子,e2echina.ti.com/.../tms320f28374s-epwmclkdiv-2-epwm-tzfrc-tzclr

您好,

在执行测试用例时的考虑因素。 F2837xD (F2837xS) 不应出现此问题。

只有 F2838x、F28P65x、F29x 器件会遇到此问题。

我已经提交了一个 JIRA 来清理这个问题。 您可以使用此测试用例来验证在清除或写入 TZFRC 后、此设备绝不会输入 IF 语句。