Part Number: TMS320F280039C

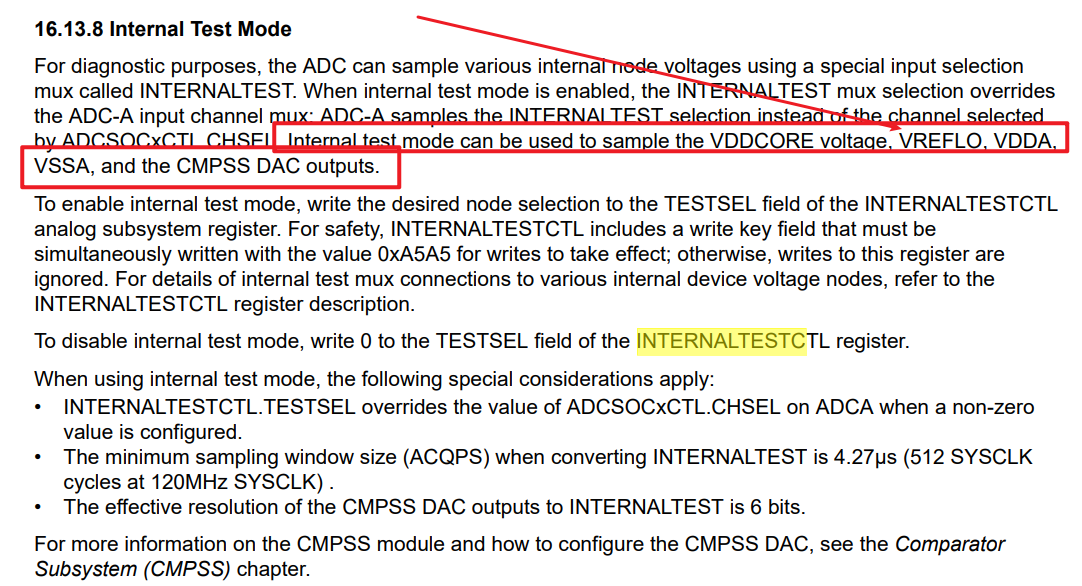

芯片手册上有下面的内容,可以对VREFLO管脚进行采样

请问可以对VREFHI管脚进行采样吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

感谢您的反馈,我理解客户的使用场景。他们说得对,按照我建议的方法,CHSEL 被旁路、任何转换都将连接到 VREFHI* 0.9。

虽然 VREFHI 没有直接的通道连接、但我有一个替代建议。

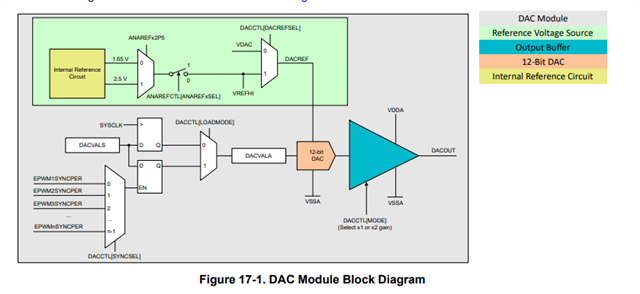

如下所示、两个内部 DAC 都以 VREFHI 引脚为基准。 它们的输出通过模拟引脚输出。

A0/B15/C15/ DACA_OUT 和 A1/B7/DACB_OUT。 客户可以将代码~3800 写入 DAC 寄存器(因此输出不会饱和)、然后对其输出进行采样。

由于客户希望查看他们在其他 ADC 采样期间是否对 VREFHI 产生干扰、因此也应显示此情况、并且 DAC 的任何增益/失调电压误差无关紧要、因为客户可以在 ADC 采样期间查看 DAC 输出与不采样或在其系统中的特定时间内的任何差异。

请告诉我这个方法是否可行。