gpioBaseAddr = (Uint32 *)&GpioDataRegs;

for (regOffset = 0; regOffset < sizeof(GpioDataRegs)/2; regOffset++)

{

gpioBaseAddr[regOffset] = 0x00000000;

}

这段寄存器清零操作,没有看懂为什么要sizeof(GpioDataRegs)/2

对应寄存器地址,没对上,求大神讲解。

GpioDataRegs是以下结构体

struct GPIO_DATA_REGS {

union GPADAT_REG GPADAT; // GPIO A Data Register (GPIO0 to 31)

union GPASET_REG GPASET; // GPIO A Data Set Register (GPIO0 to 31)

union GPACLEAR_REG GPACLEAR; // GPIO A Data Clear Register (GPIO0 to 31)

union GPATOGGLE_REG GPATOGGLE; // GPIO A Data Toggle Register (GPIO0 to 31)

union GPBDAT_REG GPBDAT; // GPIO B Data Register (GPIO32 to 63)

union GPBSET_REG GPBSET; // GPIO B Data Set Register (GPIO32 to 63)

union GPBCLEAR_REG GPBCLEAR; // GPIO B Data Clear Register (GPIO32 to 63)

union GPBTOGGLE_REG GPBTOGGLE; // GPIO B Data Toggle Register (GPIO32 to 63)

union GPCDAT_REG GPCDAT;

。。。。

}

联合体都是如下格式的成员

union GPADAT_REG {

Uint32 all;

struct GPADAT_BITS bit;

};

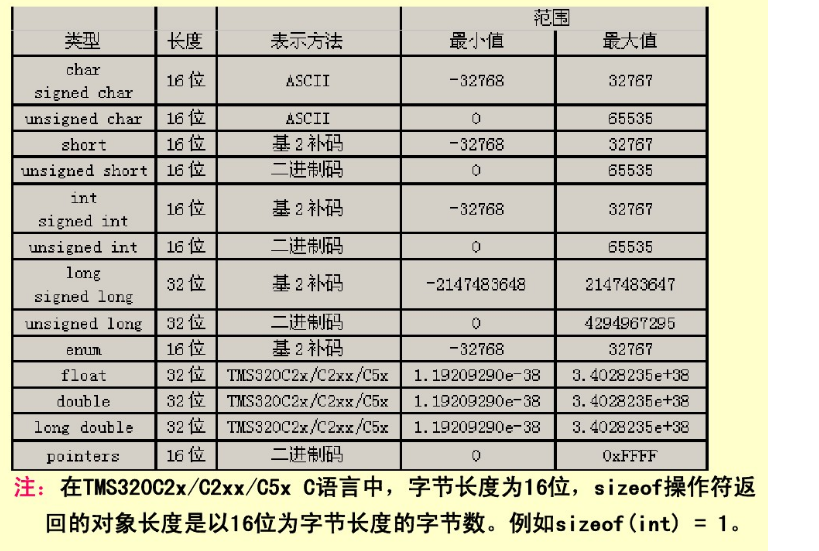

数据手册,寄存器地址,为什么寄存器地址都是偶数0 2 4。。增长,但是0h的寄存器,含有4个字节。

Offset Acronym Register Name Write Protection Section

0h GPADAT GPIO A Data Register (GPIO0 to 31) Go

2h GPASET GPIO A Data Set Register (GPIO0 to 31) Go

4h GPACLEAR GPIO A Data Clear Register (GPIO0 to 31) Go

6h GPATOGGLE GPIO A Data Toggle Register (GPIO0 to 31) Go

8h GPBDAT GPIO B Data Register (GPIO32 to 63) Go

Ah GPBSET GPIO B Data Set Register (GPIO32 to 63) Go

Ch GPBCLEAR GPIO B Data Clear Register (GPIO32 to 63) Go

Eh GPBTOGGLE GPIO B Data Toggle Register (GPIO32 to 63) Go

10h GPCDAT GPIO C Data Register (GPIO64 to 95)