在坛子上看到一个类似的帖子,但和他的情况又不完全相同,耽搁好几天了,一直没有解决:

我用的是f28335和fpga通过xintf通信,选用的是zone7,配置如下:

EALLOW;

XintfRegs.XINTCNF2.bit.XTIMCLK = 1;

// No write buffering

XintfRegs.XINTCNF2.bit.WRBUFF = 0;

// XCLKOUT is enabled

XintfRegs.XINTCNF2.bit.CLKOFF = 0;

// XCLKOUT = XTIMCLK/2

XintfRegs.XINTCNF2.bit.CLKMODE = 0;

XintfRegs.XTIMING7.bit.XWRLEAD = 2;

XintfRegs.XTIMING7.bit.XWRACTIVE = 5;

XintfRegs.XTIMING7.bit.XWRTRAIL = 2;

// Zone read timing

XintfRegs.XTIMING7.bit.XRDLEAD = 3;

XintfRegs.XTIMING7.bit.XRDACTIVE = 7;

XintfRegs.XTIMING7.bit.XRDTRAIL = 3;

// double all Zone read/write lead/active/trail timing

// XintfRegs.XTIMING7.bit.X2TIMING = 1;

XintfRegs.XTIMING7.bit.X2TIMING = 0;

// Zone will sample XREADY signal

//XintfRegs.XTIMING7.bit.USEREADY = 1;

XintfRegs.XTIMING7.bit.USEREADY = 0;

XintfRegs.XTIMING7.bit.READYMODE = 0; // sample asynchronous

// Size must be either:

// 0,1 = x32 or

// 1,1 = x16 other values are reserved

XintfRegs.XTIMING7.bit.XSIZE = 3;

// Bank switching

// Assume Zone 7 is slow, so add additional BCYC cycles

// when ever switching from Zone 7 to another Zone.

// This will help avoid bus contention.

XintfRegs.XBANK.bit.BANK = 7;

XintfRegs.XBANK.bit.BCYC = 7;

///GPIO属性配置

GpioCtrlRegs.GPCMUX1.bit.GPIO64 = 3; // XD15

GpioCtrlRegs.GPCMUX1.bit.GPIO65 = 3; // XD14

GpioCtrlRegs.GPCMUX1.bit.GPIO66 = 3; // XD13

GpioCtrlRegs.GPCMUX1.bit.GPIO67 = 3; // XD12

GpioCtrlRegs.GPCMUX1.bit.GPIO68 = 3; // XD11

GpioCtrlRegs.GPCMUX1.bit.GPIO69 = 3; // XD10

GpioCtrlRegs.GPCMUX1.bit.GPIO70 = 3; // XD19

GpioCtrlRegs.GPCMUX1.bit.GPIO71 = 3; // XD8

GpioCtrlRegs.GPCMUX1.bit.GPIO72 = 3; // XD7

GpioCtrlRegs.GPCMUX1.bit.GPIO73 = 3; // XD6

GpioCtrlRegs.GPCMUX1.bit.GPIO74 = 3; // XD5

GpioCtrlRegs.GPCMUX1.bit.GPIO75 = 3; // XD4

GpioCtrlRegs.GPCMUX1.bit.GPIO76 = 3; // XD3

GpioCtrlRegs.GPCMUX1.bit.GPIO77 = 3; // XD2

GpioCtrlRegs.GPCMUX1.bit.GPIO78 = 3; // XD1

GpioCtrlRegs.GPCMUX1.bit.GPIO79 = 3; // XD0

GpioCtrlRegs.GPBMUX1.bit.GPIO40 = 3; // XA0/XWE1n

GpioCtrlRegs.GPBMUX1.bit.GPIO41 = 3; // XA1

GpioCtrlRegs.GPBMUX1.bit.GPIO42 = 3; // XA2

GpioCtrlRegs.GPBMUX1.bit.GPIO43 = 3; // XA3

GpioCtrlRegs.GPBMUX1.bit.GPIO44 = 3; // XA4

GpioCtrlRegs.GPBMUX1.bit.GPIO45 = 3; // XA5

GpioCtrlRegs.GPBMUX1.bit.GPIO46 = 3; // XA6

GpioCtrlRegs.GPBMUX1.bit.GPIO47 = 3; // XA7

GpioCtrlRegs.GPCMUX2.bit.GPIO80 = 3; // XA8

GpioCtrlRegs.GPCMUX2.bit.GPIO81 = 3; // XA9

GpioCtrlRegs.GPCMUX2.bit.GPIO82 = 3; // XA10

GpioCtrlRegs.GPCMUX2.bit.GPIO83 = 3; // XA11

GpioCtrlRegs.GPCMUX2.bit.GPIO84 = 3; // XA12

GpioCtrlRegs.GPCMUX2.bit.GPIO85 = 3; // XA13

GpioCtrlRegs.GPCMUX2.bit.GPIO86 = 3; // XA14

GpioCtrlRegs.GPCMUX2.bit.GPIO87 = 3; // XA15

GpioCtrlRegs.GPBMUX1.bit.GPIO39 = 3; // XA16

GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 3; // XA17

GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 3; // XA18

GpioCtrlRegs.GPAMUX2.bit.GPIO29 = 3; // XA19

GpioCtrlRegs.GPBMUX1.bit.GPIO34 = 3; // XREADY

GpioCtrlRegs.GPBMUX1.bit.GPIO35 = 3; // XRNW

GpioCtrlRegs.GPBMUX1.bit.GPIO38 = 3; // XWE0

GpioCtrlRegs.GPBMUX1.bit.GPIO36 = 3; // XZCS0

GpioCtrlRegs.GPBMUX1.bit.GPIO37 = 3; // XZCS7

GpioCtrlRegs.GPAMUX2.bit.GPIO28 = 3; // XZCS6

EDIS;

asm(" RPT #7 || NOP");

写访问程序为:

Uint16 *ExRamStart = (Uint16 *)0x200000;

*(ExRamStart + 1) = 0x5a5a;

*(ExRamStart + 2) = 0x1234;

*(ExRamStart + 3) = 0xa5a5;

*(ExRamStart + 4) = 0x4321;

*(ExRamStart + 5) = 0x5678;

*(ExRamStart + 6) = 0x9abc;

*(ExRamStart + 7) = 0xcdef;

*(ExRamStart + 8) = 0xfdec;

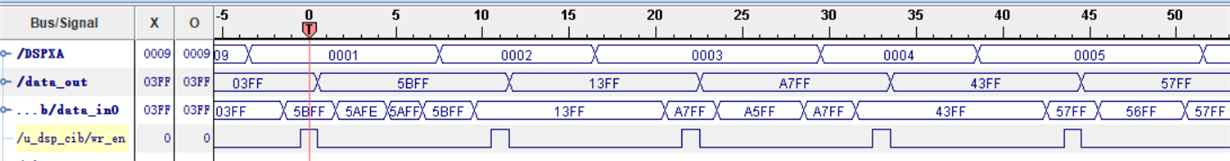

单步断点执行,在fpga端通过chipscope抓取数据,发现数据总线上的值和程序中写入的大部分时间都不一致,地址总线没有问题,回读也没有问题,DSP这边对应的配置寄存器也看了,确实和程序配置中的一致,查看memory的值也不对。写入的数据在不断的翻转,而且最终也没有程序写入的数据,这个会是什么问题呢?

能帮忙分析一下吗?谢谢!