Other Parts Discussed in Thread: TMDSHSECDOCK, TMDSCNCD280025C, TMS320F280025, TMS320F280025C, C2000WARE

Received tmdscncd280025c + tmdshsecdock package On December 9, the outer package is very standard.

TMDSCNCD280025C is a low-cost evaluation and development board for TI C2000™ MCU series of F280025C devices.

TMDSHSECDOCK is a baseboard that provides header pin access to key signals on compatible HSEC180-based controlCARDs. A breadboard area is available for rapid prototyping. Board power can be provided by the provided USB cable or a 5V barrel supply.

The following will introduce the parameter performance of TMS320f280025、TMDSCNCD280025C and TMDSHSECDOCK for reference of performance evaluation and debugging. The part 5 of this document will introduce how to use C2000 CLB to realize PWM output phase shift and protection function.

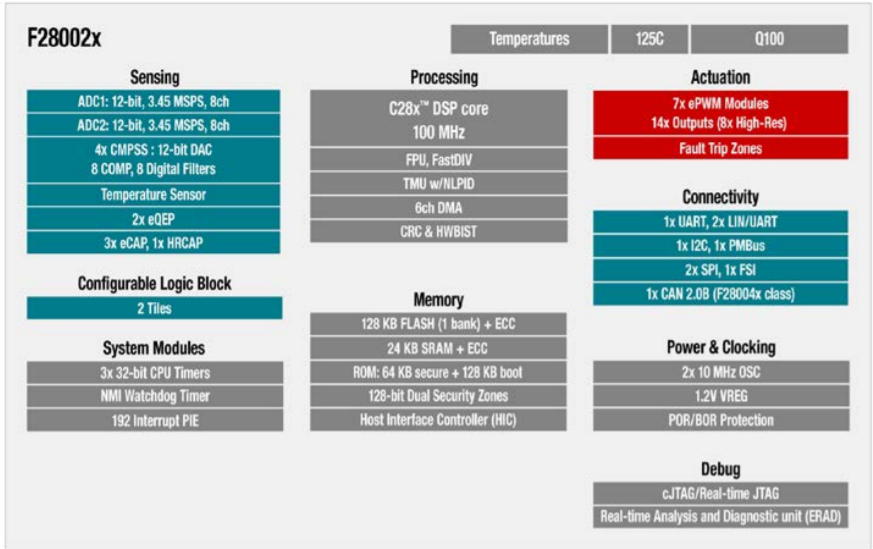

1 TMS320F280025 performance description

Reference technical documentation

- TMS320F28002x Real-Time Microcontrollers

Basic performance Introduction:

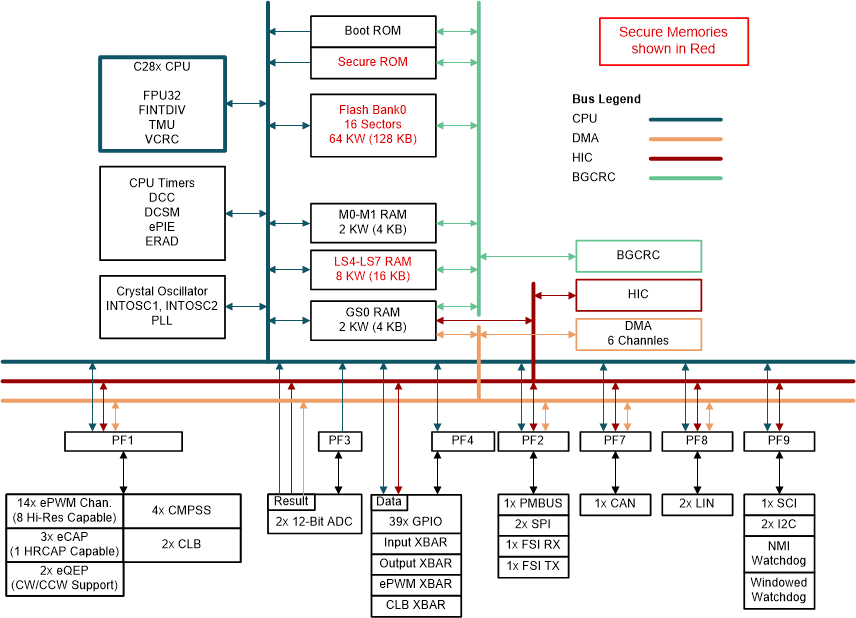

The Functional Block Diagram shows the CPU system and associated peripherals.

Figure 1-1. Functional Block Diagram

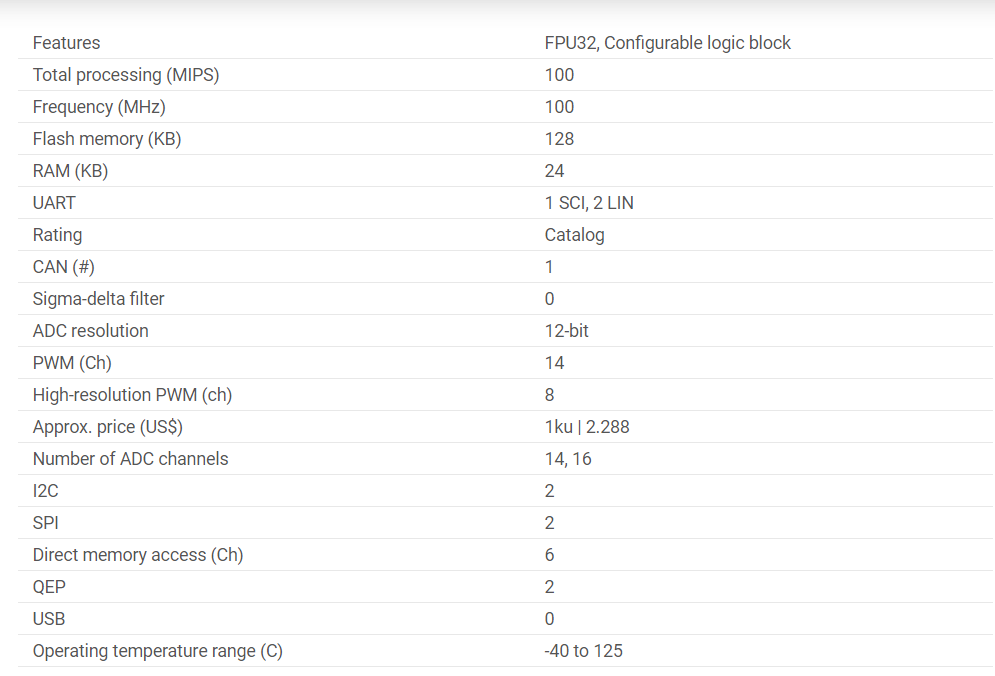

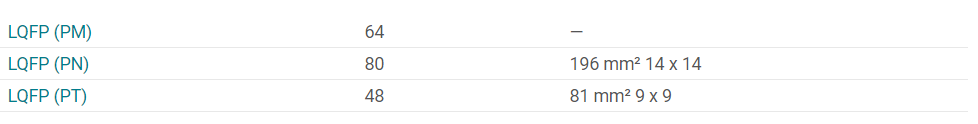

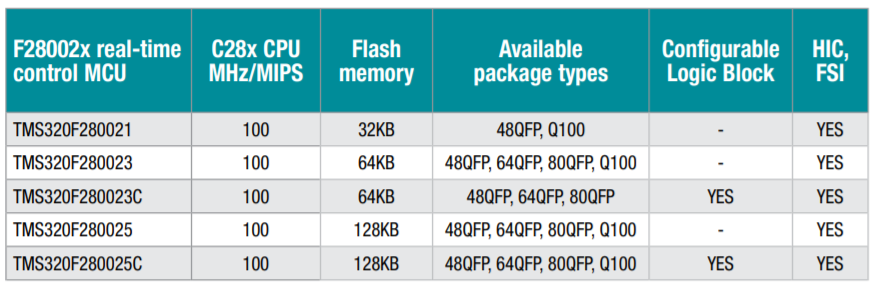

Device Comparison

Package:

- TMS320C28x 32-bit DSP core at 100 MHz

- IEEE 754 Floating-Point Unit (FPU)

- Support for Fast Integer Division (FINTDIV)

- Trigonometric Math Unit (TMU)

- Support for Nonlinear Proportional Integral Derivative (NLPID) control

- CRC Engine and Instructions (VCRC)

- Ten hardware breakpoints (with ERAD)

- On-chip memory

- 128KB (64KW) of flash (ECC-protected)

- 24KB (12KW) of RAM (ECC or parity-protected)

- Dual-zone security

- Clock and system control

- Two internal zero-pin 10-MHz oscillators

- On-chip crystal oscillator or external clock input

- Windowed watchdog timer module

- Missing clock detection circuitry

- Dual-clock Comparator (DCC)

- Single 3.3-V supply

- Internal VREG generation

- Brownout reset (BOR) circuit

- System peripherals

- 6-channel Direct Memory Access (DMA) controller

- 39 individually programmable multiplexed General-Purpose Input/Output (GPIO) pins

- 16 digital inputs on analog pins

- Enhanced Peripheral Interrupt Expansion (ePIE)

- Multiple low-power mode (LPM) support

- Embedded Real-time Analysis and Diagnostic (ERAD)

- Unique Identification (UID) number

- Communications peripherals

- One Power-Management Bus (PMBus) interface

- Two Inter-integrated Circuit (I2C) interfaces

- One Controller Area Network (CAN) bus port

- Two Serial Peripheral Interface (SPI) ports

- One UART-compatible Serial Communication Interface (SCI)

- Two UART-compatible Local Interconnect Network (LIN) interfaces

- Fast Serial Interface (FSI) with one transmitter and one receiver (up to 200Mbps)

- Analog system

- Two 3.45-MSPS, 12-bit Analog-to-Digital Converters (ADCs)

- Up to 16 external channels

- Four integrated Post-Processing Blocks (PPB) per ADC

- Four windowed comparators (CMPSS) with 12-bit reference Digital-to-Analog Converters (DACs)

- Digital glitch filters

- Enhanced control peripherals

- 14 ePWM channels with eight channels that have high-resolution capability (150-ps resolution)

- Integrated dead-band support

- Integrated hardware trip zones (TZs)

- Three Enhanced Capture (eCAP) modules

- High-resolution Capture (HRCAP) available on one of the three eCAP modules

- Two Enhanced Quadrature Encoder Pulse (eQEP) modules with support for CW/CCW operation modes

- Configurable Logic Block (CLB)

- Augments existing peripheral capability

- Supports position manager solutions

- Host Interface Controller (HIC)

- Access to internal memory from an external host

- Background CRC (BGCRC)

- One cycle CRC computation on 32 bits of data

- Diagnostic features

- Memory Power On Self Test (MPOST)

- Hardware Built-in Self Test (HWBIST)

- Package options:

- 80-pin Low-profile Quad Flatpack (LQFP) [PN suffix]

- 64-pin LQFP [PM suffix]

- 48-pin LQFP [PT suffix]

- Temperature options:

- S: –40°C to 125°C junction

- Q: –40°C to 125°C free-air (AEC Q100 qualification for automotive applications)

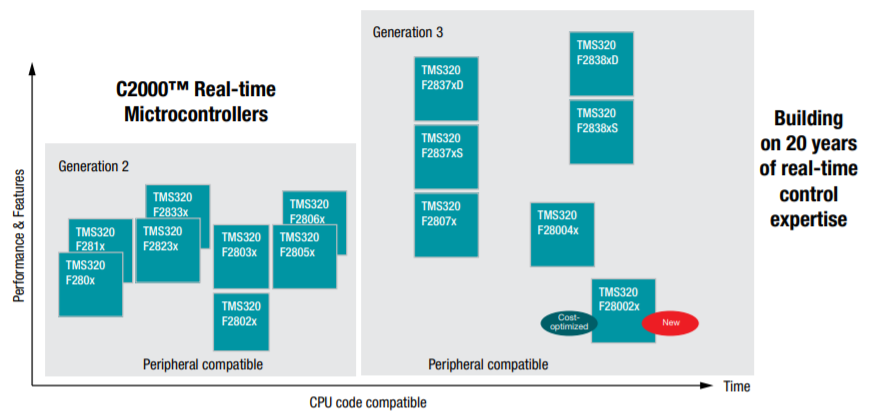

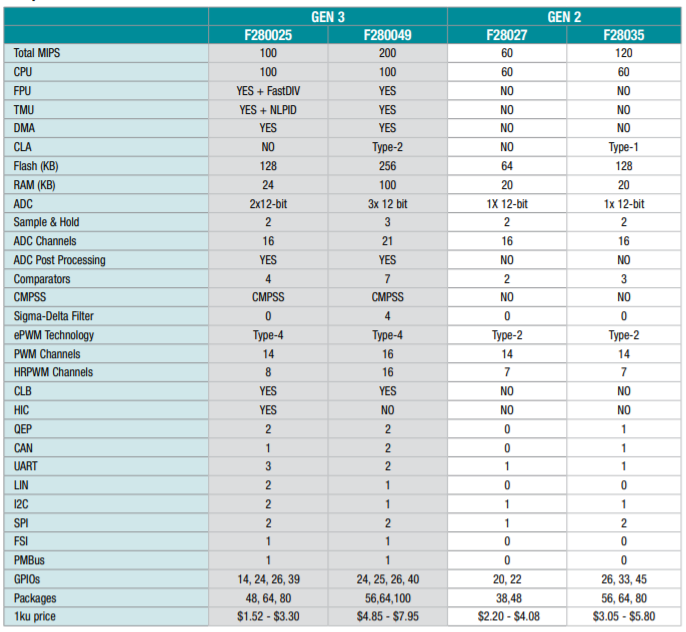

2 Comparison between tms320f280025c and the same type of C2000 series chip:

Comparison of F28002x series with Gen 2 and Gen 3 series

F28002x series:Cost-optimized built for power conversion applications.

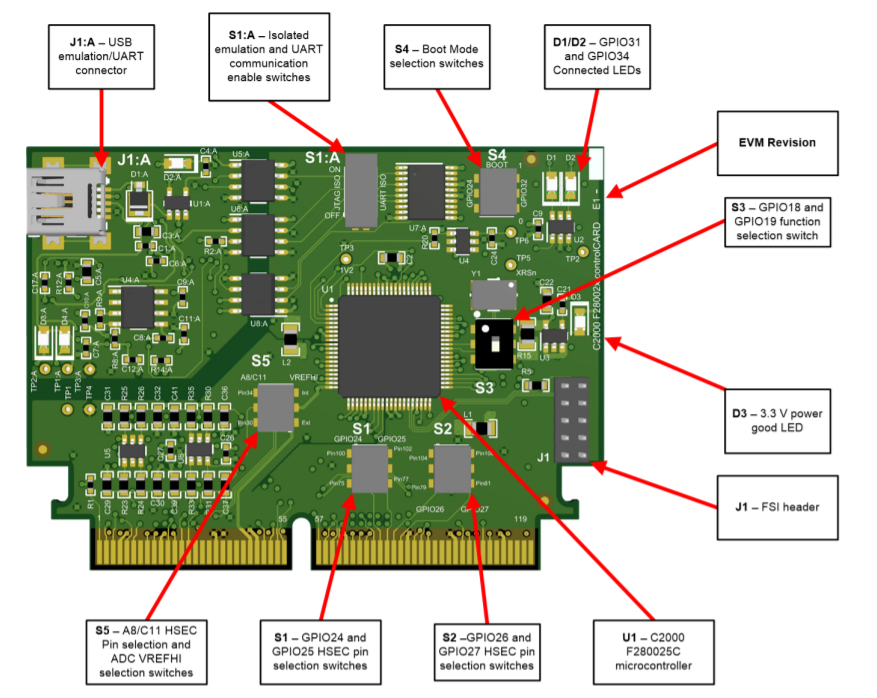

3 F280025 controlCARD Information:(TMDSCNCD280025C)

Reference technical documentation :

- F280025 controlCARD Information Guide.

Introduction:

Figure2_1. F280025 controlCARD

Each controlCARD comes with a Hardware Developer’s Kit, which is a full set of files necessary to evaluate and develop with a C2000 device. These files include:

- Schematics – Designed in Altium

- Bill of Materials (BOM)

- Layout PCB files - Designed in Altium

- Gerber files

Notes: This kit is designed to explore the functionality of the F28002x microcontroller. The controlCARD can be treated as a good reference design; it is not intended to be a complete customer design. Full compliance to safety, EMI/EMC, and other regulations are left to the designer of the customer’s system.

Hardware Features

- Isolated on-board XDS100v2 USB-to-JTAG debug probe enables real-time in-system programming and debugging

- Standard 180-pin controlCARD HSEC interface

- Analog I/O, digital I/O and JTAG signals at card interface

- Hardware Files are in C2000Ware at boards\controlCARDs\TMDSCNCD280025C

Software Features

- Free download of Code Composer Studio IDE

- Free download of C2000Ware for device drivers and example projects

- DigitalPower SDK and powerSUITE

- MotorControl SDK

- MathWorks Embedded Target Support

- solidThinking Embed Support

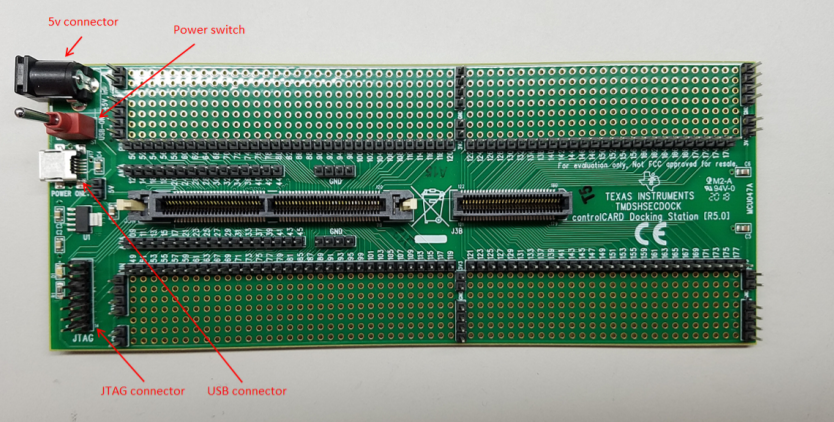

2 180-Pin ControlCARD Docking Station Information(TMDSHSECDOCK )

Reference technical documentation :

- 180-Pin ControlCARD Docking Station Information Guide

- 180_HSEC8_DV_pinout_R1_1.pdf shows GPIO mapping.(The design files are located in C2000ware in the C:\ti\c2000\C2000Ware_1_00_04_00\boards\ExperimenterKits\DockingStation_ HSEC_120or180pin\R4_1 directory. )

Introduction

Figure 3_1. 180-Pin controlCARD Docking Station

2 Using C2000 CLB to realize PWM output phase shift and protection function (TMDSCNCD280025C +TMDSHSECDOCK )

Reference technical documentation :

- TMS320F28002x Real-Time Microcontrollers Technical Reference Manual

- C2000WARE_INSTALL_LOCATION\utilities\clb_tool\clb_syscfg\doc

Compiling environment of C2000 Real-time MCUs

- Code Composer Studio (CCS) Integrated Development Environment (IDE)(https://www.ti.com/tool/download/CCSTUDIO)

In order to simulate the CLB design the following additional external (non-TI) tools must be installed:

• A GNU compiler (TDM-GCC)(https://sourceforge.net/projects/tdm-gcc/files/TDMGCC%20Installer/tdm64-gcc-5.1.0-2.exe/download.)

• A simulation viewer (GTK Wave)(https://sourceforge.net/projects/gtkwave/files/)

Firmware:

#include "driverlib.h"

#include "device.h"

#include "clb_config.h"

#include "clb.h"

#include "inc/hw_epwm.h"

#define EPWM1_TIMER_TBPRD 1500U

#define EPWM1_CMPA 50U

#define EPWM1_CMPB 50U

#define EPWM2_TIMER_TBPRD 1500U

#define EPWM2_CMPA 50U

#define EPWM2_CMPB 50U

void initEPWM1(void);

void initEPWM2(void);

__interrupt void epwm1ISR(void);

uint16_t g_u16_Fault_Protection = 0;

uint32_t mode = 0;

void main(void)

{

Device_init();

Device_initGPIO();

Interrupt_initModule();

Interrupt_initVectorTable();

Interrupt_register(INT_EPWM1, &epwm1ISR);

GPIO_setPadConfig(0, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_0_EPWM1A);

GPIO_setPadConfig(1, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_1_EPWM1B);

GPIO_setPadConfig(2, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_2_EPWM2A);

GPIO_setPadConfig(3, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_3_EPWM2B);

SysCtl_disablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

initEPWM1();

initEPWM2();

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLB1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLB2);

// initialize all CLB tiles

CLB_enableCLB(CLB1_BASE);

CLB_enableCLB(CLB2_BASE);

initTILE1(CLB1_BASE);

initTILE2(CLB2_BASE);

// CLB tile 1 configuration

CLB_configLocalInputMux(CLB1_BASE, CLB_IN0, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN1, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN2, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN3, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN4, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN5, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN6, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN7, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN0, CLB_GLOBAL_IN_MUX_EPWM1A);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN1, CLB_GLOBAL_IN_MUX_EPWM1A);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN2, CLB_GLOBAL_IN_MUX_EPWM1B);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN3, CLB_GLOBAL_IN_MUX_EPWM1B);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN4, CLB_GLOBAL_IN_MUX_EPWM1_CTRDIR);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN5, CLB_GLOBAL_IN_MUX_EPWM1_CTRDIR);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN6, CLB_GLOBAL_IN_MUX_EPWM1_CTRDIR);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN7, CLB_GLOBAL_IN_MUX_EPWM1_CTRDIR);

CLB_configGPInputMux(CLB1_BASE, CLB_IN0, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN1, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN2, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN3, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN4, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB1_BASE, CLB_IN5, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB1_BASE, CLB_IN6, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB1_BASE, CLB_IN7, CLB_GP_IN_MUX_GP_REG);

//CLB_selectInputFilter(CLB1_BASE, CLB_IN0, CLB_FILTER_FALLING_EDGE);

// CLB_selectInputFilter(CLB1_BASE, CLB_IN2, CLB_FILTER_FALLING_EDGE);

CLB_selectInputFilter(CLB1_BASE, CLB_IN0, CLB_FILTER_RISING_EDGE);

CLB_selectInputFilter(CLB1_BASE, CLB_IN2, CLB_FILTER_FALLING_EDGE);

// CLB tile 2 configuration

CLB_configLocalInputMux(CLB2_BASE, CLB_IN0, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN1, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN2, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN3, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN4, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN5, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN6, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB2_BASE, CLB_IN7, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN0, CLB_GLOBAL_IN_MUX_EPWM2A);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN1, CLB_GLOBAL_IN_MUX_EPWM2A);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN2, CLB_GLOBAL_IN_MUX_EPWM2B);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN3, CLB_GLOBAL_IN_MUX_EPWM2B);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN4, CLB_GLOBAL_IN_MUX_EPWM2_CTRDIR);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN5, CLB_GLOBAL_IN_MUX_EPWM2_CTRDIR);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN6, CLB_GLOBAL_IN_MUX_EPWM2_CTRDIR);

CLB_configGlobalInputMux(CLB2_BASE, CLB_IN7, CLB_GLOBAL_IN_MUX_EPWM2_CTRDIR);

CLB_configGPInputMux(CLB2_BASE, CLB_IN0, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB2_BASE, CLB_IN1, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB2_BASE, CLB_IN2, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB2_BASE, CLB_IN3, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB2_BASE, CLB_IN4, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB2_BASE, CLB_IN5, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB2_BASE, CLB_IN6, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB2_BASE, CLB_IN7, CLB_GP_IN_MUX_GP_REG);

// CLB_selectInputFilter(CLB2_BASE, CLB_IN0, CLB_FILTER_FALLING_EDGE);

// CLB_selectInputFilter(CLB2_BASE, CLB_IN2, CLB_FILTER_FALLING_EDGE);

CLB_selectInputFilter(CLB2_BASE, CLB_IN0, CLB_FILTER_RISING_EDGE);

CLB_selectInputFilter(CLB2_BASE, CLB_IN2, CLB_FILTER_FALLING_EDGE);

// start PWMs

EPWM_setTimeBaseCounterMode(EPWM1_BASE, EPWM_COUNTER_MODE_UP_DOWN);

EPWM_setTimeBaseCounterMode(EPWM2_BASE, EPWM_COUNTER_MODE_UP_DOWN);

Interrupt_enable(INT_EPWM1);

EINT;

while(1)

{

asm(" NOP");

if (g_u16_Fault_Protection== 1)

{

EPWM_setActionQualifierContSWForceAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A,EPWM_AQ_SW_OUTPUT_LOW);

EPWM_setActionQualifierContSWForceAction(EPWM1_BASE,EPWM_AQ_OUTPUT_B,EPWM_AQ_SW_OUTPUT_LOW);

EPWM_setActionQualifierContSWForceAction(EPWM2_BASE, EPWM_AQ_OUTPUT_A,EPWM_AQ_SW_OUTPUT_LOW);

EPWM_setActionQualifierContSWForceAction(EPWM2_BASE,EPWM_AQ_OUTPUT_B,EPWM_AQ_SW_OUTPUT_LOW);

}

else

{

EPWM_setActionQualifierContSWForceAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A,EPWM_AQ_SW_DISABLED);

EPWM_setActionQualifierContSWForceAction(EPWM1_BASE,EPWM_AQ_OUTPUT_B,EPWM_AQ_SW_DISABLED);

EPWM_setActionQualifierContSWForceAction(EPWM2_BASE, EPWM_AQ_OUTPUT_A,EPWM_AQ_SW_DISABLED);

EPWM_setActionQualifierContSWForceAction(EPWM2_BASE,EPWM_AQ_OUTPUT_B,EPWM_AQ_SW_DISABLED);

}

}

}

void initEPWM1()

{

EPWM_setTimeBasePeriod(EPWM1_BASE, EPWM1_TIMER_TBPRD);

EPWM_setPhaseShift(EPWM1_BASE, 0U);

EPWM_setTimeBaseCounter(EPWM1_BASE, 0U);

EPWM_enableSyncOutPulseSource(EPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_CNTR_ZERO);

EPWM_setCounterCompareValue(EPWM1_BASE, EPWM_COUNTER_COMPARE_A, EPWM1_CMPA);

EPWM_setCounterCompareValue(EPWM1_BASE, EPWM_COUNTER_COMPARE_B, EPWM1_CMPB);

EPWM_disablePhaseShiftLoad(EPWM1_BASE);

EPWM_setClockPrescaler(EPWM1_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setInterruptSource(EPWM1_BASE, EPWM_INT_TBCTR_ZERO);

EPWM_enableInterrupt(EPWM1_BASE);

EPWM_setInterruptEventCount(EPWM1_BASE, 3U);

}

void initEPWM2()

{

EPWM_setTimeBasePeriod(EPWM2_BASE, EPWM2_TIMER_TBPRD);

EPWM_setPhaseShift(EPWM2_BASE, 0U);

EPWM_setTimeBaseCounter(EPWM2_BASE, 0U);

EPWM_enablePhaseShiftLoad(EPWM2_BASE);

EPWM_setPhaseShift(EPWM2_BASE, 0U);

EPWM_setCounterCompareValue(EPWM2_BASE, EPWM_COUNTER_COMPARE_A, EPWM2_CMPA);

EPWM_setCounterCompareValue(EPWM2_BASE, EPWM_COUNTER_COMPARE_B, EPWM2_CMPB);

EPWM_setClockPrescaler(EPWM2_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setCounterCompareShadowLoadMode(EPWM2_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM2_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(EPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(EPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(EPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(EPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

}

__interrupt void epwm1ISR(void)

{

EPWM_clearEventTriggerInterruptFlag(EPWM1_BASE);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

if (mode == 0)

{

CLB_setOutputMask(CLB1_BASE, 0x5, false);

CLB_setOutputMask(CLB1_BASE, 0x4, false);

CLB_setOutputMask(CLB2_BASE, 0x5, false);

CLB_setOutputMask(CLB2_BASE, 0x4, false);

}

else

{

CLB_setOutputMask(CLB1_BASE, 0x5, true);

CLB_setOutputMask(CLB1_BASE, 0x4, true);

CLB_setOutputMask(CLB2_BASE, 0x5, true);

CLB_setOutputMask(CLB2_BASE, 0x4, true);

}

asm(" NOP");

}

/* end of file */

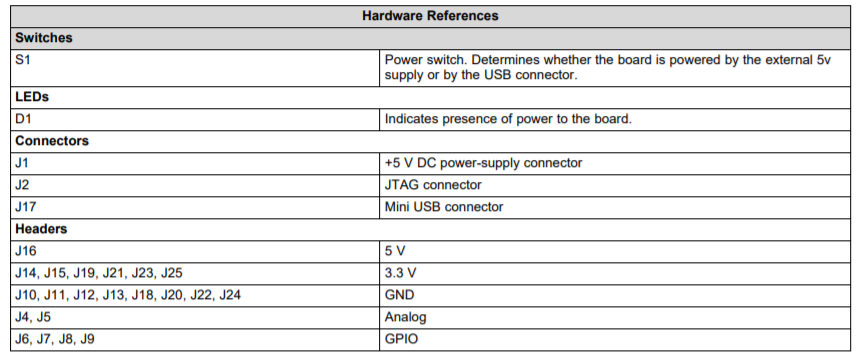

Logic of CLB:

PWM frequency:66.7Khz

PWM duty:0.0333

Dead time:0.2us

Phase shift angle:165°

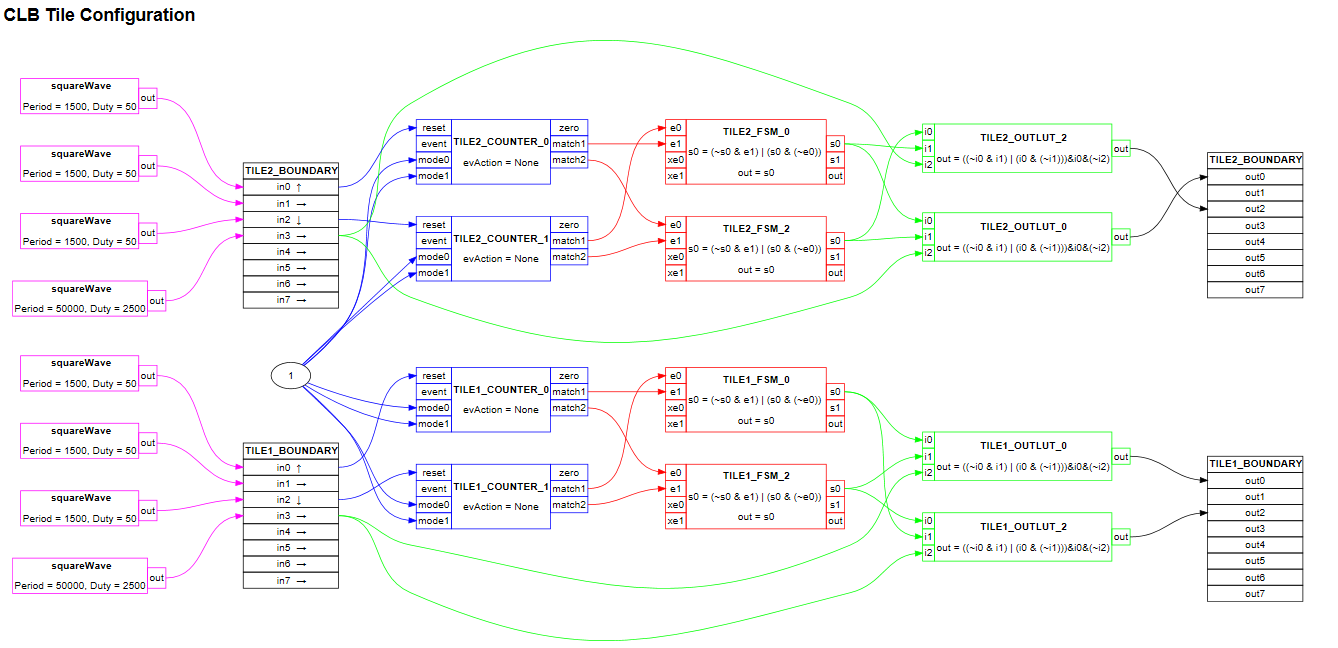

The simulation results are as follows: