Other Parts Discussed in Thread: C2000WARE

你好:

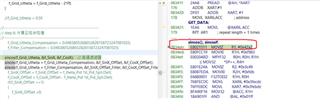

在调用fpu32_fast_supplement库中的void sincos(float32 radian, float32* PtrSin, float32* PtrCos);进行计算的时候,结果异常,于是单步进行分析。

在调用这个函数的时候,有这样的信息提示:Can't find a source file at "/home/ubnuser/ti/c2000ware/libraries/math/temp/source/fpu32/sincos_f32.asm"

Locate the file or edit the source lookup path to include its location.

然后单步执行,发现在执行这个函数的时候程序跳转到地址0x08314eb

感觉这个地址异常,没有在FPUmathTables,于是查找map文件,这个函数的地址确实是0x0834eb

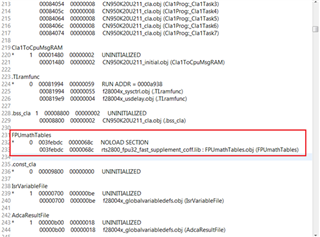

然后查找FPUmathTables的地址,认为这个地址应该是正常的

认为sincos应该在FPUmathTables中,但是没有

关于这个计算错误的现象,能不能给点建议,多谢

。

。