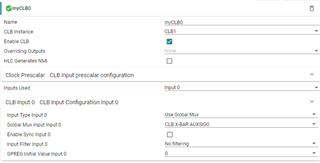

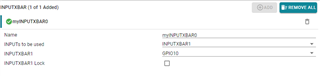

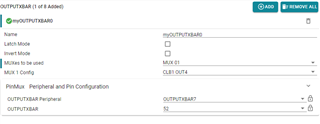

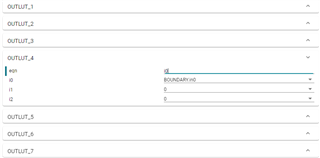

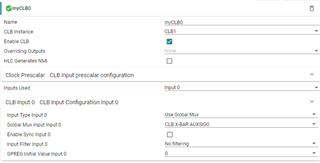

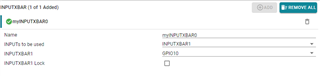

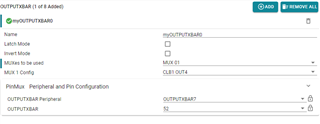

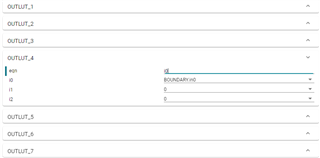

将脉冲信号通过GPIO输入,利用Input x-bar路由到output x-bar 后,可以在GPIO输出得到相同的脉冲信号,但是中间经过CLB,将Input x-bar输入给clb x-bar 后送入CLB模块input0,然后直连通过CLB1OUT4输出到output x-bar 后,在GPIO输出得到的信号一直是低电平,两种方式都是烧录到Flash中运行,请问有什么地方有问题?相关配置如下,感觉没有发现什么问题

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

将脉冲信号通过GPIO输入,利用Input x-bar路由到output x-bar 后,可以在GPIO输出得到相同的脉冲信号,但是中间经过CLB,将Input x-bar输入给clb x-bar 后送入CLB模块input0,然后直连通过CLB1OUT4输出到output x-bar 后,在GPIO输出得到的信号一直是低电平,两种方式都是烧录到Flash中运行,请问有什么地方有问题?相关配置如下,感觉没有发现什么问题

您是否有参考过下面文档的 9 输入 X-BAR、输出 X-BAR 和 CLB X-BAR?

您现在使用的是哪个cmd呢?在RAM下是否可以成功运行?目前好像没有在flash下运行的cmd文件以及例程。我之后会和同事确认一下

在E2E上有相关的讨论,您可以看一下

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/809543/ccs-tms320f28379d-urgent-clb-not-work-when-running-from-flash/2996543?tisearch=e2e-sitesearch&keymatch=clb%252525252525252520cmd%252525252525252520flash#2996543

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x0000F4, length = 0x00030C

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE /* on-chip Flash */

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x001000 /* on-chip Flash */

/* BANK 1 */

FLASH_BANK1_SEC0 : origin = 0x090000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC1 : origin = 0x091000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC2 : origin = 0x092000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC3 : origin = 0x093000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC4 : origin = 0x094000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC5 : origin = 0x095000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC6 : origin = 0x096000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC7 : origin = 0x097000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC8 : origin = 0x098000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC9 : origin = 0x099000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC10 : origin = 0x09A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC11 : origin = 0x09B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC12 : origin = 0x09C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC13 : origin = 0x09D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC14 : origin = 0x09E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC15 : origin = 0x09F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK1_SEC15_RSVD : origin = 0x09FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x0000F1 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x002000

RAMGS1 : origin = 0x00E000, length = 0x002000

RAMGS2 : origin = 0x010000, length = 0x002000

RAMGS3 : origin = 0x012000, length = 0x001FF8

// RAMGS3_RSVD : origin = 0x013FF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

}

SECTIONS

{

codestart : > BEGIN, PAGE = 0, ALIGN(4)

.text : >>FLASH_BANK0_SEC1 | FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3, PAGE = 0, ALIGN(4)

.cinit : > FLASH_BANK0_SEC1, PAGE = 0, ALIGN(4)

.pinit : > FLASH_BANK0_SEC1, PAGE = 0, ALIGN(4)

.switch : > FLASH_BANK0_SEC1, PAGE = 0, ALIGN(4)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

.cio : > RAMLS0, PAGE = 0

.stack : > RAMM1, PAGE = 1

.ebss : > RAMLS5, PAGE = 1

.esysmem : > RAMLS5, PAGE = 1

.econst : >> FLASH_BANK0_SEC4 | FLASH_BANK0_SEC5, PAGE = 0, ALIGN(4)

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMLS0 | RAMLS1 | RAMLS2 |RAMLS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

这是我用的CMD文件,您在帮我看下有问题?谢谢!