Part Number: TMS320F28335

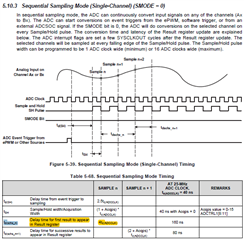

28335 TRM数据手册中 ADC部分有如下描述

按照Table的描述 25MHz ADCCLK条件下 只需要1个ADC时钟就完成了对采样电压的转换 如图中高亮的部分 我的理解对吗 请问是如何实现这样短的时间就完成转换的呢?

对比28035 采样保持结束后 需要13个ADC时钟才能完成转换 二者的差别看起来还是挺大的

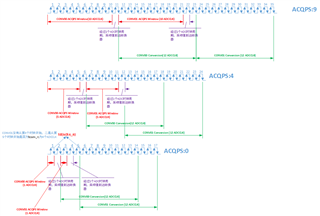

28335 TRM中有如下时序图

这个图里 对 Soff的描述中提到"until the sampled voltage is

passed to the converter."

从这里的意思看 采样保持结束后的1个ADC时钟 是把采样电压传送到ADC Converter的时间 传送给转换器和转换完成应该不是一个概念吧

请问采样保持结束后的一个ADC CLK 到底是指ADC转换会在这1和时钟周期内完成

还是指着这一个时钟周期 是采样保持完成后采样电压经过一个时钟周期到达转换器