Other Parts Discussed in Thread: C2000WARE

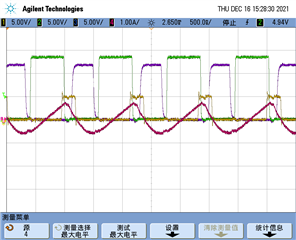

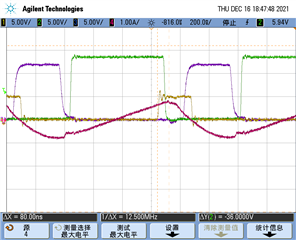

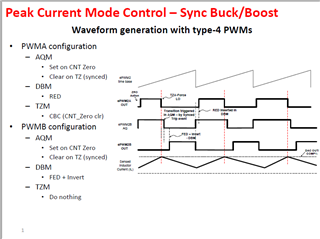

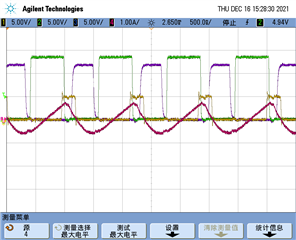

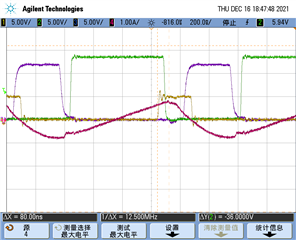

按照下图3进行配置,下面是我电路的实际波形,绿色是PWM1A的驱动,紫色是PWM1B的驱动,黄色是引出的CTRIPOUT信号,现在有个问题 ,PWM1A是设置的TZA.FORCE LOW 动作,但是可以看到CTRIP信号到来时,经过了一定时间的延时,PWM1A才关断,延时时间好像跟我设置的DBRED(80ns)差不多,但是理论上TZA不经过DB的呀,不该有这个延时呀。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

按照下图3进行配置,下面是我电路的实际波形,绿色是PWM1A的驱动,紫色是PWM1B的驱动,黄色是引出的CTRIPOUT信号,现在有个问题 ,PWM1A是设置的TZA.FORCE LOW 动作,但是可以看到CTRIP信号到来时,经过了一定时间的延时,PWM1A才关断,延时时间好像跟我设置的DBRED(80ns)差不多,但是理论上TZA不经过DB的呀,不该有这个延时呀。

你好,你测试的是CMPSS模块控制TZ模块拉低PWMA吗?看波形似乎看不出两者有什么动作关系啊。TZ是one ***?关键两种模式似乎都跟图片上的波形对不起了啊

有没有参考过TI例程:C:\ti\c2000\C2000Ware_4_00_00_00\driverlib\f2837xd\examples\cpu1\epwm

// Included Files

//pin define Cmpss3 CMP3IN_P to B2 vo_sense to A1 改EPWM6的话 ADC soc信号要改 EPWMENCK信号要改 TRIP路径EPWM bar ET事件 低输入时不正常

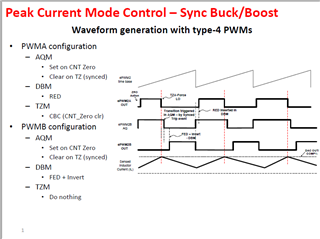

//PWM1A TZA-FORCE LO 1B 在AQ中 T1事件动作通过同步TRIP EVENT

#include "F28x_Project.h"

// Defines

//

//definitions for selecting DACH reference

#define REFERENCE_VDDA 0

#define REFERENCE_VDAC 1

//definitions for COMPH input selection

#define NEGIN_DAC 0

#define NEGIN_PIN 1

//definitions for CTRIPH/CTRIPOUTH output selection

#define CTRIP_ASYNCH 0

#define CTRIP_SYNCH 1

#define CTRIP_FILTER 2

#define CTRIP_LATCH 3

int i=0;

//ADC定义

#define Vo_ref 2470 //12V 2460

float Vo_ave=0;

#define chanel 1

#define acqps 29 //采样窗 (acqps+1)*sysclk *5ns

//斜坡定义

#define slopeval 10 /* Required slope compensation */

#define dacval 8000

//

// Function Prototypes

//

void InitAdc(void);

void InitCMPSS(void);

void InitEPWM(void);

void pid_init(void);

interrupt void adc_isr(void);

//

// Main

//

void main(void)

{

//

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the F2837xD_SysCtrl.c file.

//

InitSysCtrl();

//

// Step 2. Initialize GPIO:

// This example function is found in the F2837xD_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

//

InitGpio();

//

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the F2837xD_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

/* DSP28377D_PieVect.c */

InitPieVectTable();

/* Interrupt re-mapped to ISR function */

EALLOW;

PieVectTable.ADCA1_INT = &adc_isr;

EDIS;

InitAdc();

/* Enable ADCA1INT1 in PIE */

PieCtrlRegs.PIEIER1.bit.INTx1 = 1;/* Enable INT 1.1 in the PIE */

IER |= M_INT1;/* Enable CPU Interrupt 1 */

EINT;/* Enable Global interrupt INTM */

ERTM;/* Enable Global realtime interrupt DBGM */

// Configure Comparator COMP3H to accept POS input from pin and NEG input

// from DAC

InitEPWM();

InitEPwm1Gpio();

InitCMPSS();

// Configure GPIO5() to output OUTPUTXBAR3

//

GPIO_SetupPinMux(5, GPIO_MUX_CPU1, 3);

//观察ctripout值 gpio5

// Configure COMP3 to feed TRIP4 EPWM DC trip input

//

pid_init();

while(1)

{

;

}

}

//

// InitCMPSS - Initialize CMPSS3 and configure settings

//

void InitAdc(void)

{

//ADC时钟开启

EALLOW;

CpuSysRegs.PCLKCR13.bit.ADC_A=1;

EDIS;

EALLOW;

AdcaRegs.ADCCTL2.bit.PRESCALE = 6; //set ADCCLK divider to /4

AdcSetMode(ADC_ADCA, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);

AdcaRegs.ADCSOC0CTL.bit.CHSEL =chanel; //SOC0 will convert ADCINA1

AdcaRegs.ADCSOC0CTL.bit.ACQPS = acqps; //SOC0 will use sample duration of 20 SYSCLK cycles

AdcaRegs.ADCSOC0CTL.bit.TRIGSEL = 5; //SOC0 will begin conversion on ePWM1 SOCA 5 EPWM1A

AdcaRegs.ADCSOC1CTL.bit.CHSEL =chanel; //SOC0 will convert ADCINA1

AdcaRegs.ADCSOC1CTL.bit.ACQPS = acqps; //SOC0 will use sample duration of 20 SYSCLK cycles

AdcaRegs.ADCSOC1CTL.bit.TRIGSEL = 5; //SOC0 will begin conversion on ePWM1 SOCA

AdcaRegs.ADCSOC2CTL.bit.CHSEL =chanel; //SOC0 will convert ADCINA1

AdcaRegs.ADCSOC2CTL.bit.ACQPS = acqps; //SOC0 will use sample duration of 20 SYSCLK cycles

AdcaRegs.ADCSOC2CTL.bit.TRIGSEL = 5; //SOC0 will begin conversion on ePWM1 SOCA

AdcaRegs.ADCSOC3CTL.bit.CHSEL =chanel; //SOC0 will convert ADCINA1

AdcaRegs.ADCSOC3CTL.bit.ACQPS = acqps; //SOC0 will use sample duration of 20 SYSCLK cycles

AdcaRegs.ADCSOC3CTL.bit.TRIGSEL = 5; //SOC0 will begin conversion on ePWM1 SOCA

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 0; //end of SOC0 will set INT1 flag

AdcaRegs.ADCINTSEL1N2.bit.INT1E = 1; //enable INT1 flag

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //make sure INT1 flag is cleared

//Set pulse positions to late

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1;

//power up the ADC

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1;

//delay for 1ms to allow ADC time to power up

DELAY_US(1000);

EDIS;

}

void InitCMPSS(void)

{

EALLOW;

CpuSysRegs.PCLKCR14.bit.CMPSS3 = 0; //禁用时钟

//将CMPSS分配给CPU1

DevCfgRegs.CPUSEL12.bit.CMPSS3 = 0;

CpuSysRegs.PCLKCR14.bit.CMPSS3 = 1; //启用时钟

EDIS;

EALLOW;

//

//Enable CMPSS

//

Cmpss3Regs.COMPCTL.bit.COMPDACE = 1;

//NEG signal comes from DAC

//

Cmpss3Regs.COMPCTL.bit.COMPHSOURCE = NEGIN_DAC;

//

//Use VDDA as the reference for DAC

//

Cmpss3Regs.COMPDACCTL.bit.SELREF = REFERENCE_VDDA; //VDDA的值是多少 3.3

//选择同步或异步比较器触发

// Cmpss3Regs.COMPCTL.bit.ASYNCHEN = 0; //High comparator asynchronous path enable. Allows asynchronous comparator output to feed into OR gate with latched digital filter signal when CTRIPHSEL=3 or CTRIPOUTHSEL=3

//

// Configure CTRIPOUT path

// Asynch output feeds CTRIPH and CTRIPOUTH

//

Cmpss3Regs.COMPCTL.bit.COMPHINV=0; // 0比较器同相输出 1 比较器反相输出

//配置数字滤波器

//最大SAMPWIN值提供最大数量的样本(5位)

Cmpss3Regs.CTRIPHFILCTL.bit.SAMPWIN = 20 ; // 0x1F & 0x00;

//最大THRESH值需要整个窗口的静态值

//(5 位 THRESH 应该大于 SAMPWIN 的一半)

Cmpss3Regs.CTRIPHFILCTL.bit.THRESH = 17 ; //0x1F & 0x01

//最大 CLKPRESCALE 值提供样本之间的最长时间(12 位)

Cmpss3Regs.CTRIPHFILCLKCTL.bit.CLKPRESCALE =2 ; //234 2 10 7 0x3FF & 0x001;

//重置过滤逻辑并开始过滤

Cmpss3Regs.CTRIPHFILCTL.bit.FILINIT = 1;

//清除锁存器

Cmpss3Regs.COMPSTSCLR.bit.HSYNCCLREN=1; //1 EPWMSYNCPER will reset latch

Cmpss3Regs.COMPSTSCLR.bit.HLATCHCLR = 1; //清除锁存值

//输出路径

Cmpss3Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_ASYNCH;

// Cmpss3Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_FILTER;

Cmpss3Regs.COMPCTL.bit.CTRIPOUTHSEL = CTRIP_ASYNCH;

// Cmpss3Regs.COMPCTL.bit.CTRIPOUTHSEL = CTRIP_FILTER;

// Cmpss3Regs.COMPHYSCTL.bit.COMPHYS=2; //设置 滞环宽度

//同步清除使能

// Cmpss3Regs.COMPSTSCLR.bit.HSYNCCLREN = 1;

//

// Configure CTRIPOUTH output pin

// Configure OUTPUTXBAR3 to be CTRIPOUT1H

//

OutputXbarRegs.OUTPUT3MUX0TO15CFG.bit.MUX4 = 0;

//

//Enable OUTPUTXBAR3 Mux for Output

//

OutputXbarRegs.OUTPUT3MUXENABLE.bit.MUX4 = 1;

//

//DAC source select. Determines whether DACHVALA is updated from DACHVALS or from the ramp generator

//

Cmpss3Regs.COMPDACCTL.bit.DACSOURCE = 1; // 0 DAC updated from DACHVALS, 1 DAC updated from the ramp generator

Cmpss3Regs.COMPDACCTL.bit.RAMPLOADSEL=1; //斜坡加载模式 Ramp load select. Determines whether RAMPSTS is updated from RAMPMAXREFA or RAMPMAXREFS when COMPSTS[COMPHSTS] is triggered.

Cmpss3Regs.COMPDACCTL.bit.SWLOADSEL=1; /*Software load select. Determines whether DACxVALA is updated

from DACxVALS on SYSCLK or EPWMSYNCPER.

0 DACxVALA is updated from DACxVALS on SYSCLK

1 DACxVALA is updated from DACxVALS on EPWMSYNCPER

*/

//

//Ramp generator source select. Determines which EPWMSYNCPER signal is used within the CMPSS module

//

Cmpss3Regs.COMPDACCTL.bit.RAMPSOURCE = 0; // 0 EPWM1SYNCPER, 3 EPWM4SYNCPER 更改EPWM需要修改 Ramp generator source select. Determines which EPWMSYNCPER

// signal is used within the CMPSS module

EDIS;

Cmpss3Regs.RAMPDECVALS = slopeval;

// Cmpss3Regs.RAMPMAXREFS = dacval; //2048==> 2048/16 *3.3(ref) /4096=dacout 0.07

}

//

// InitEPWM - Initialize EPWM1 module settings

//

void InitEPWM(void)

{

EALLOW;

// ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV=1; //EPWM分频器

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

//

//Configure EPWM to run at SYSCLK

//

// ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV = 0;

EPwm1Regs.TBCTL.bit.CLKDIV = 0;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;

//Initialize dummy values for EPWM CTR/PRD

//

EPwm1Regs.TBCTR = 0;

EPwm1Regs.TBPRD = 117; // 850kHz PWM

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading禁止计数器装载相位寄存器的值

EPwm1Regs.TBPHS.bit.TBPHS= 0;/* Set Phase register to zero */

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; // Sync down-stream module

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //影子装载模式

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero在CTR=0时,影子寄存器装载

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

//Configure TRIP4 to be CTRIP3H

//

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX4 = 0; // 0.4 是CMPSS3的CTRIPH

//Enable TRIP4 Mux for Output

//

EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX4 = 1;

// Enable PWM

//

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;

EPwm1Regs.CMPA.bit.CMPA =95; //max duty limit 97/117 考虑了死区 0.82最大占空比

EPwm1Regs.CMPB.bit.CMPB =95; //max duty limit 97/117 考虑了死区 0.82最大占空比

// Set actions AQ也配置 实际上A是通过跳闸

//

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // Set PWM1A on event A, up count

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; // Clear PWM1A on event A, up count 限制最大占空比防止一直高电平

// EPwm1Regs.AQCTLA2.bit.T1U = AQ_CLEAR; // Action when event occurs on T2 in UP-Count

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET; // Set PWM1B on event B, up count

EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR; // Set PWM1B on event B, up count 最小占空比限制

EPwm1Regs.AQCTLB2.bit.T1U = AQ_CLEAR; // Action when event occurs on T2 in UP-Count 1:DCAEVT2发生时动作

EPwm1Regs.AQTSRCSEL.bit.T1SEL = 3; // 0:DCAEVT1, 1:DCAEVT2, 2:DCBEVT1, 3:DCBEVT2 有TI T2事件 DCAEVT2事件被配置为异步跳闸 能否应用于B的T1事件触发

//

//---------------------------- Active Low PWMs - Setup Deadband

//

// EPwm1Regs.DBCTL.bit.HALFCYCLE = 1; // Half cycle clocking enabled

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.DEDB_MODE=0;

//EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBCTL.bit.IN_MODE =DBA_RED_DBB_FED; //A RED B FED+invert

EPwm1Regs.DBRED.bit.DBRED = 8; //死区时间 DBFED × TTBCLK(10nS @100Mhz)

EPwm1Regs.DBFED.bit.DBFED = 10;

//-----ET------------------------触发ADC采样-----------------------

EPwm1Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on A group */

EPwm1Regs.ETSEL.bit.SOCASEL =1; //001: Enable event time-base counter equal to zero. (TBCTR = 0x00)

EPwm1Regs.ETPS.bit.SOCPSSEL = 1; //EPWMxSOC A/B Pre-Scale Selection Bits 预分频

// EPwm1Regs.ETPS.bit.INTPSSEL=1; //EPWM int中断

// EPwm1Regs.ETPS.bit.SOCAPRD=1;

EPwm1Regs.ETSOCPS.bit.SOCAPRD2 = 4; /* Generate pulse on 6st event */

// EPwm1Regs.ETCLR.bit.SOCA=1; //清除SOCA中断标志位

EPwm1Regs.TZSEL.bit.DCAEVT2 = 1; // Enable DCAEVT2 as a CBC trip source for this ePWM module

EPwm1Regs.TZCBCCLR.bit.DCAEVT2 = 1; // Clear Flag for Digital Compare Output A Event 2 selected for CBC

EPwm1Regs.TZCLR.bit.DCAEVT2=1 ; // Clear Flag for Digital Compare Output A Event 2

// 0: Writing 0 has no effect. This bit always reads back 0.

// 1: Writing 1 clears the DCAEVT2 event trip condition.

EPwm1Regs.TZCLR.bit.CBC=1 ; //Clear Flag for Cycle-By-Cycle (CBC) Trip Latch 清除中断标志TZFLG

// 0: Has no effect. Always reads back a 0.

// 1: Clears this Trip (set) condition.

EPwm1Regs.TZCLR.bit.CBCPULSE=0; //00: CTR = zero pulse clears CBC trip latch. (Same as legacy designs.)

//------------------B通道 DCBEVT2--------------------------------------

// EPwm1Regs.TZSEL.bit.DCBEVT2 = 1; // Enable DCAEVT2 as a CBC trip source for this ePWM module

// EPwm1Regs.TZCBCCLR.bit.DCBEVT2 = 1; // Clear Flag for Digital Compare Output A Event 2 selected for CBC

// EPwm1Regs.TZCLR.bit.DCBEVT2=1 ; //

// EPwm1Regs.TZCLR.bit.CBCPULSE=0; //00: CTR = zero pulse clears CBC trip latch. (Same as legacy designs.)

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO; /* EPWM1A will go low 这是锁存的*/

// EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO;/* EPWM1B will go low */

EPwm1Regs.TZCTL.bit.TZB = TZ_NO_CHANGE; /* EPWM1B has no action 在AQ中动作*/

// EPwm1Regs.TZCTL.bit.DCAEVT2 = TZ_FORCE_LO; // 10: Force EPWMxA to a low state 保护不用 通过T1 T2事件进行动作 可以避免直通 这是不锁存的

// EPwm1Regs.TZCTL.bit.DCBEVT2 = TZ_NO_CHANGE; // 11: Do Nothing, trip action is disabled

// EPwm1Regs.TZCTL.bit.DCAEVT2 = TZ_NO_CHANGE; //屏蔽DCA B动作 采用TZAB动作

// EPwm1Regs.TZCTL2.bit.ETZE = 1; //0: Use trip action from TZCTL (legacy EPWM compatibility) 1: Use trip action defined in TZCTL2, TZCTLDCA and TZCTLDCB. Settings in TZCTL are ignored

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 3; // Trip IN4 3

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 3; // Trip 4 3

EPwm1Regs.TZDCSEL.bit.DCAEVT2 = TZ_DCAH_HI; /*000: Event disabled DCAH为高 产生一个DCAEVT2事件

001: DCAH = low, DCAL = don't care

010: DCAH = high, DCAL = don't care

011: DCAL = low, DCAH = don't care

100: DCAL = high, DCAH = don't care

101: DCAL = high, DCAH = low */

EPwm1Regs.TZDCSEL.bit.DCBEVT2 = TZ_DCBH_HI; //TRIP4 产生DCAH与DCBH事件,DCAH配置CBC跳闸触发TZA ,DCBH配置为事件T1 用于B pwm

EPwm1Regs.DCACTL.bit.EVT2SRCSEL =1; // 0: Source Is DCAEVT2 Signal; 1: Source Is DCEVTFILT Signal TZ路径

EPwm1Regs.DCACTL.bit.EVT2FRCSYNCSEL =1; // 0: Source is synchronized with EPWMCLK; 1: Source is passed through asynchronously 通过sync生成DCAEVT2.FORCE

EPwm1Regs.DCBCTL.bit.EVT2SRCSEL =0; // 0: Source Is DCBEVT2 Signal; 1: Source Is DCEVTFILT Signal

EPwm1Regs.DCBCTL.bit.EVT2FRCSYNCSEL = 1; // 0: Source is synchronized with EPWMCLK; 1: Source is passed through asynchronously

//---空窗设置---事件过滤--可不配置--------------------------------------------------------------------------

EPwm1Regs.DCFCTL.bit.SRCSEL = 1; // 01: Source Is DCAEVT2 Signal

EPwm1Regs.DCFCTL.bit.BLANKE = 1; // 1: Blanking window is enabled

EPwm1Regs.DCFCTL.bit.BLANKINV = 0; // 0: Blanking window not inverted; 1: Blanking window inverted

EPwm1Regs.DCFCTL.bit.PULSESEL = 1; // 01: Time-base counter equal to zero

//PWMSYNCSEL

EPwm1Regs.HRPCTL.bit.PWMSYNCSELX = 0; // EPWMSYNCPER is defined by PWMSYNCSEL 0 EPWM1

EPwm1Regs.HRPCTL.bit.PWMSYNCSEL = 1; // 1:CTR = zero; 0:CTR = PRD

EDIS;

EPwm1Regs.DCFOFFSET =0;

EPwm1Regs.DCFWINDOW = 20; //DCFWINDOW*TB_WINDOW(10nS @100Mhz)

}

struct pid{

double err; //定义偏差值

double err_last; //定义上一个偏差值

double err_pre; //定义上上一个偏差值

double Kp,Ki,Kd; //定义比例,积分,微分系数

double det_err_pi;

double out_pi;

} pid;

//初始化变量

void pid_init()

{

pid.err=0;

pid.err_last=0;

pid.err_pre=0;

pid.Kp=1.2; //kp=0.05;ki=0.01 PI参数调节 0.02 0.0015

pid.Ki=0.05;

// pid.Kd=1;

pid.out_pi=0; //初始duty

pid.det_err_pi=0;

}

interrupt void adc_isr(void)

{

// i++;

// GpioDataRegs.GPASET.bit.GPIO12 = 1;/* Set GPIO12 (for timing purposes) */

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;/* Clr ADCINT1 flag for next SOC */

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;/* Acknowledge interrupt to PIE */

Vo_ave=((AdcaResultRegs.ADCRESULT0)+(AdcaResultRegs.ADCRESULT1)+(AdcaResultRegs.ADCRESULT2)+(AdcaResultRegs.ADCRESULT3))>>2;

pid.err=Vo_ref-Vo_ave;

pid.err=0.5*(pid.err+pid.err_last);

if (pid.err<=5&&pid.err>=-5)

pid.err=0;

pid.out_pi=pid.out_pi+pid.Kp*(pid.err-pid.err_last)+pid.Ki*pid.err;

pid.err_last=pid.err;

if (pid.out_pi<0)

pid.out_pi=0;

if (pid.out_pi>65530)

pid.out_pi=65530;

Cmpss3Regs.RAMPMAXREFS=(pid.out_pi); //左移4位 DAC为12位 RAMPMAXREFS的高12位to DACHVALA 所以要左移4位

// GpioDataRegs.GPACLEAR.bit.GPIO12 = 1;/* Set GPIO12 (for timing purposes) */

// ; //观察i值,判断有无进入中断

return;

}

/****************************************************************************

// No more.

****************************************************************************/

你好,因为我对CMPSS模块的掌握度也不高,所以需要将你的问题升级到英文E2E论坛。但由于现在是美国的节假日期间,没有工程师支持。需要等到1月3日之后才会有工程师开始接管论坛。需要麻烦你在1月3日之后再整理一个帖子发布一下新帖,到时候为你升级。(因为旧贴可能被刷下去,新帖的话系统有提示)